# Design Techniques for Low Power Mixed Analog-Digital Circuits with Application to Smart Wireless Systems

by

## Said Fares Al-Sarawi

B.E. (First Class Honours), Arab Academy for Science and Technology, Alexandria, Egypt, 1990

Thesis submitted for the degree of

## **Doctor of Philosophy**

in

School of Electrical and Electronic Engineering Faculty of Engineering, Computer and Mathematical Sciences

> The University of Adelaide Australia

> > February, 2003

© Copyright 2003 Said Fares Al-Sarawi All Rights Reserved

Typeset in  $\Join \mathbf{T}_{\mathbf{E}} \mathbf{X} \, \mathbf{2}_{\mathcal{E}}$

# Contents

| Content              | s                                      |

|----------------------|----------------------------------------|

| Abstrac              | ix ix                                  |

| Declarat             | cion xi                                |

| Publicat             | ions xiii                              |

| Acknow               | ledgement xix                          |

| List of I            | igures xxi                             |

| List of <sup>-</sup> | Tables xxix                            |

| List of /            | Abbreviations and Symbols xxxi         |

| Chapter              | 1. Introduction and Motivation 1       |

| 1.1                  | Mixed Signal Systems                   |

| 1.2                  | Low Power Mixed Signal Technology      |

| 1.3                  | Problem Definition                     |

| 1.4                  | Common Mixed Analog-Digital Components |

| 1.5                  | Original Contributions                 |

| 1.6                  | Thesis Structure                       |

| BIBLIO               | GRAPHY 17                              |

| Chapter              | 2. Controlled Gain Amplifiers 25       |

| 2.1                  | Introduction                           |

| 2.2                  | Series Transistor Configuration        |

| 2.3                  | Parallel Transistor Configuration      |

| 2.4                  | Current Mirror Configuration           |

Page iii

| 2.5    | Digitally Programmable Conductance Configuration         | 41                   |

|--------|----------------------------------------------------------|----------------------|

| 2.6    | Biasing Circuits                                         | 45                   |

| 2.7    | Experimental Work                                        | 48                   |

|        | 2.7.1 Measurement of the STC Amplifier                   | 48                   |

|        | 2.7.2 Measurement of the PTC Amplifier                   | <del>1</del> 0<br>51 |

| 2.8    | Summary                                                  | 55                   |

|        |                                                          | 00                   |

| BIBLI  | OGRAPHY                                                  | 59                   |

| Chapt  | er 3. Digital Trimming of Operational Amplifiers         | 61                   |

| 3.1    | Introduction                                             | 62                   |

| 3.2    | Statistical Data on Input Offset Voltage                 | 63                   |

|        | 3.2.1 Components of $\mathbf{V}_{os}$                    | 63                   |

|        | 3.2.2 Statistical Data on $\mathbf{V}_{os}$              | 63                   |

| 3.3    | Input Offset Voltage Reduction and Cancellation          | 65                   |

|        | 3.3.1 Device Mismatch Reduction                          | 66                   |

|        | 3.3.2 Off-Chip Offset Voltage Compensation               | 66                   |

|        | 3.3.3 Auto-zero Cancellation Techniques                  | 67                   |

| 3.4    | New Digital Trimming Techniques                          | 70                   |

|        | 3.4.1 Weighted-Voltage Trimming Technique                | 71                   |

|        | 3.4.2 Weighted-Current Trimming Technique                | 76                   |

| 3.5    | Experimental Work                                        | 80                   |

| 3.6    | Summary                                                  | 82                   |

| BIBLIC | OGRAPHY                                                  | 89                   |

| Chapte | er 4. New Schmitt Trigger Circuits                       | 93                   |

| 4.1    | Introduction                                             | 94                   |

| 4.2    |                                                          | 97                   |

|        | 4.2.1 An nMOS Schmitt Trigger                            |                      |

|        | 4.2.2 A pMOS Schmitt Trigger                             |                      |

|        | 4.2.3 Fully Symmetrical CMOS Schmitt Trigger             |                      |

|        | 4.2.4 Fully Adjustable Hysteresis CMOS Schmitt Trigger 1 |                      |

| 4.3    | Finite Input Impedance (FII) Schmitt Trigger             |                      |

|        | 4.3.1 Resistive FII Schmitt Trigger                      |                      |

|        | 4.3.2 Fully Adjustable FII Schmitt Trigger               |                      |

|        | 4.3.3 Self-Biased FII Schmitt Trigger                    |                      |

|        |                                                          |                      |

| 4.4 | Experimental Work |

|-----|-------------------|

| 4.5 | Discussion        |

| 4.6 | Summary           |

### **BIBLIOGRAPHY**

### 133

| Chapter | 5. An   | alog Circuit Design using Neuron MOS           | 137 |

|---------|---------|------------------------------------------------|-----|

| 5.1     | Introdu | action                                         | 138 |

| 5.2     | Genera  | l Model Derivation of the $\nu$ MOS Transistor | 139 |

| 5.3     | Key De  | esign Parameters for $\nu$ MOS Transistor      | 141 |

|         | 5.3.1   | Floating-Gate Gain Factor                      | 141 |

|         | 5.3.2   | Threshold Voltage Seen from the Floating Gate  | 142 |

|         | 5.3.3   | Floating Gate Offset Voltage                   | 142 |

| 5.4     | Analog  | Circuit Design using $\nu$ MOS Transistor      | 143 |

|         | 5.4.1   | A Linear Grounded Resistor                     | 143 |

|         | 5.4.2   | Controlled Gain Amplifiers                     | 145 |

|         | 5.4.3   | Schmitt Trigger Circuits                       | 151 |

| 5.5     | Power 2 | Dissipation Reduction                          | 154 |

| 5.6     | Experie | mental Work                                    | 155 |

| 5.7     | Summa   | ary                                            | 157 |

|         |         |                                                |     |

### BIBLIOGRAPHY

### 163

| Chapter | 6. Novel Low Power Ripple Through Gray Code Counters             | 167 |

|---------|------------------------------------------------------------------|-----|

| 6.1     | Introduction                                                     | 168 |

| 6.2     | Gray Code Sequence Generation                                    | 169 |

| 6.3     | Formulas Implementation                                          | 171 |

|         | 6.3.1 Formulas implementation using JK flip-flops                | 172 |

|         | 6.3.2 Formulas implementation using a dynamic D-flip-flops       | 172 |

| 6.4     | Experimental Work                                                | 176 |

| 6.5     | Summary                                                          | 176 |

| BIBLIO  | GRAPHY                                                           | 185 |

| Chapter | 7. A Novel Topology for Grounded-to-Floating Resistor Conversion | 187 |

| 7.1     | Introduction                                                     | 188 |

7.2

A New Circuit Topology

188

7.2.1

Theoretical Analysis

188

|    |       | 7.2.2 Topology Implementation                         | 190 |

|----|-------|-------------------------------------------------------|-----|

|    | 7.3   | Converting a Grounded Resistor to a Floating Resistor |     |

|    | 7.4   | Very High Value Floating (VHVF) Resistor              |     |

|    | 7.5   | Statistical Modelling                                 |     |

|    | 7.6   | A Design Example                                      |     |

|    | 7.7   | Summary                                               |     |

| BI | BLIC  | GRAPHY                                                | 207 |

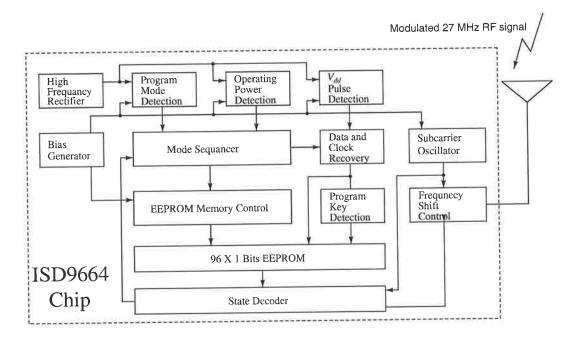

| Cł | napte | r 8. Program Mode Detection Circuits                  | 209 |

|    | 8.1   | Introduction                                          | 210 |

|    | 8.2   | ISD9664 Chip                                          | 211 |

|    | 8.3   | Early work on the PMD circuit                         |     |

|    |       | 8.3.1 Early Program Mode Detection Circuit            | 213 |

|    | 8.4   | New PMD circuits                                      | 215 |

|    |       | 8.4.1 New Program Mode Detection Circuits             | 217 |

|    |       | 8.4.2 PMD Circuits with a Supply Voltage Bleed        | 218 |

|    |       | 8.4.3 PMD Circuit with Node Reset                     | 223 |

|    |       | 8.4.4 Symmetrical PMD Circuit                         |     |

|    | 8.5   | Experimental Work                                     |     |

|    | 8.6   | Summary                                               | 230 |

| BI | BLIO  | GRAPHY                                                | 233 |

| Ch | aptei | 9. Conclusions and Directions                         | 235 |

|    | 9.1   | Summary and Future Directions                         | 236 |

|    | 9.2   | Research Contributions                                | 241 |

|    | 9.3   | Closing Comments                                      | 243 |

| Ap | pend  | ix A. Three Dimensional VLSI Packaging Study          | 245 |

|    | A.1   | Introduction                                          | 246 |

|    | A.2   | Advantages of 3D Packaging Technology                 | 246 |

|    |       | A.2.1 Size and Weight                                 | 246 |

|    |       | A.2.2 Silicon Efficiency                              | 247 |

|    |       | A.2.3 Delay                                           | 247 |

|    |       | A.2.4 Noise                                           |     |

|    |       | A.2.5 Power Consumption                               | 249 |

|    |       |                                                       |     |

|                                                                         | A.2.6                                                                                                    | Speed                                                                                               | 250                                                                                                                             |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                                                         | A.2.7                                                                                                    | Interconnect Capacity                                                                               | 250                                                                                                                             |

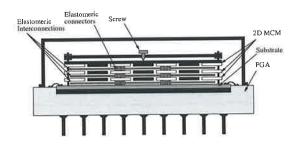

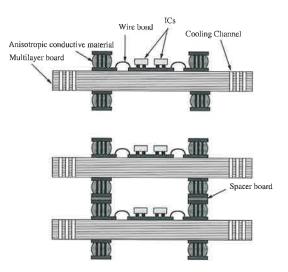

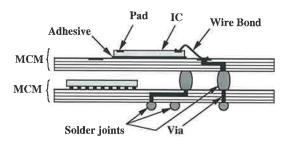

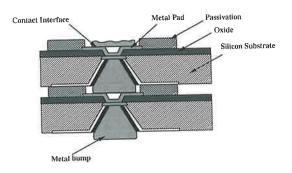

| A.3                                                                     | Vertica                                                                                                  | l Interconnections in 3D Electronics                                                                | 250                                                                                                                             |

|                                                                         | A.3.1                                                                                                    | Periphery Interconnection between Stacked ICs                                                       | 251                                                                                                                             |

|                                                                         | A.3.2                                                                                                    | Area Interconnection between Stacked ICs $\ .$                                                      | 255                                                                                                                             |

|                                                                         | A.3.3                                                                                                    | Periphery Interconnection between Stacked MCMs $\ .$                                                | 256                                                                                                                             |

|                                                                         | A.3.4                                                                                                    | Area Interconnection between Stacked MCMs $\ \ldots \ \ldots \ \ldots \ \ldots$                     | 257                                                                                                                             |

| A.4                                                                     | Limita                                                                                                   | tions of 3D Packaging Technology                                                                    | 267                                                                                                                             |

|                                                                         | A.4.1                                                                                                    | Thermal Management                                                                                  | 267                                                                                                                             |

|                                                                         | A.4.2                                                                                                    | Design complexity                                                                                   | 268                                                                                                                             |

|                                                                         | A.4.3                                                                                                    | Cost                                                                                                | 269                                                                                                                             |

|                                                                         | A.4.4                                                                                                    | Time to Delivery                                                                                    | 269                                                                                                                             |

|                                                                         | A.4.5                                                                                                    | Design Software                                                                                     | 269                                                                                                                             |

| A.5                                                                     | Discus                                                                                                   | $\operatorname{sion}$                                                                               | 270                                                                                                                             |

| A.6                                                                     | Conclu                                                                                                   | isions                                                                                              | 272                                                                                                                             |

| BIBLIO                                                                  | GRAP                                                                                                     | НҮ                                                                                                  | 277                                                                                                                             |

| Appendix B. Symmetrical Level 13 Model Parameters 285                   |                                                                                                          |                                                                                                     |                                                                                                                                 |

| Append                                                                  | ix B. S                                                                                                  | Symmetrical Level 13 Model Parameters                                                               | 285                                                                                                                             |

|                                                                         |                                                                                                          | Symmetrical Level 13 Model Parameters<br>A Statistical Analysis of MOS Mismatch                     | 285<br>289                                                                                                                      |

|                                                                         | lix C. A                                                                                                 | A Statistical Analysis of MOS Mismatch                                                              |                                                                                                                                 |

| Append<br>BIBLIO                                                        | lix C. /                                                                                                 | A Statistical Analysis of MOS Mismatch                                                              | 289                                                                                                                             |

| Append<br>BIBLIO<br>Append                                              | lix C. A<br>OGRAP<br>lix D. N                                                                            | A Statistical Analysis of MOS Mismatch                                                              | 289<br>293<br>295                                                                                                               |

| Append<br>BIBLIO<br>Append<br>D.1                                       | lix C. A<br>OGRAP<br>lix D. M<br>Introd                                                                  | A Statistical Analysis of MOS Mismatch<br>HY<br>/ery Low Frequency, Low Power Oscillators           | <ul> <li>289</li> <li>293</li> <li>295</li> </ul>                                                                               |

| Append<br>BIBLIO<br>Append<br>D.1                                       | lix C. A<br>OGRAP<br>lix D. M<br>Introd<br>Schmi                                                         | A Statistical Analysis of MOS Mismatch<br>HY<br>/ery Low Frequency, Low Power Oscillators<br>uction | <ul> <li>289</li> <li>293</li> <li>295</li> <li>296</li> </ul>                                                                  |

| Append<br>BIBLIO<br>Append<br>D.1<br>D.2<br>D.3                         | lix C. A<br>GRAP<br>lix D. V<br>Introd<br>Schmi<br>Extend                                                | A Statistical Analysis of MOS Mismatch<br>HY<br>/ery Low Frequency, Low Power Oscillators<br>uction | <ul> <li>289</li> <li>293</li> <li>295</li> <li>295</li> <li>296</li> <li>298</li> </ul>                                        |

| Append<br>BIBLIO<br>Append<br>D.1<br>D.2<br>D.3                         | lix C. A<br>GRAP<br>lix D. V<br>Introd<br>Schmi<br>Extend                                                | A Statistical Analysis of MOS Mismatch<br>HY<br>/ery Low Frequency, Low Power Oscillators<br>uction | <ul> <li>289</li> <li>293</li> <li>295</li> <li>296</li> <li>298</li> <li>300</li> </ul>                                        |

| Append<br>BIBLIO<br>Append<br>D.1<br>D.2<br>D.3                         | lix C. A<br>GRAP<br>lix D. V<br>Introd<br>Schmi<br>Extend<br>Experi                                      | A Statistical Analysis of MOS Mismatch<br>HY<br>/ery Low Frequency, Low Power Oscillators<br>uction | <ul> <li>289</li> <li>293</li> <li>295</li> <li>296</li> <li>298</li> <li>300</li> <li>300</li> </ul>                           |

| Append<br>BIBLIO<br>Append<br>D.1<br>D.2<br>D.3                         | lix C. A<br>GRAP<br>lix D. V<br>Introd<br>Schmi<br>Extend<br>Exper:<br>D.4.1<br>D.4.2                    | A Statistical Analysis of MOS Mismatch<br>HY<br>/ery Low Frequency, Low Power Oscillators<br>uction | <ul> <li>289</li> <li>293</li> <li>295</li> <li>296</li> <li>298</li> <li>300</li> <li>300</li> <li>300</li> </ul>              |

| Append<br>BIBLIO<br>Append<br>D.1<br>D.2<br>D.3<br>D.4                  | lix C. A<br>GRAP<br>lix D. V<br>Introd<br>Schmir<br>Extend<br>Exper:<br>D.4.1<br>D.4.2<br>Summ           | A Statistical Analysis of MOS Mismatch HY /ery Low Frequency, Low Power Oscillators uction          | <ul> <li>289</li> <li>293</li> <li>295</li> <li>296</li> <li>298</li> <li>300</li> <li>300</li> <li>300</li> </ul>              |

| Append<br>BIBLIO<br>Append<br>D.1<br>D.2<br>D.3<br>D.4<br>D.5<br>BIBLIO | lix C. A<br>GRAP<br>lix D. V<br>Introd<br>Schmir<br>Extend<br>Extend<br>Exper:<br>D.4.1<br>D.4.2<br>Summ | A Statistical Analysis of MOS Mismatch HY /ery Low Frequency, Low Power Oscillators uction          | <ul> <li>289</li> <li>293</li> <li>295</li> <li>296</li> <li>298</li> <li>300</li> <li>300</li> <li>300</li> <li>303</li> </ul> |

Index

315

# Abstract

This dissertation presents and discusses new design techniques for mixed analog-digital circuits with emphases on low power and small area for standard low-cost CMOS VLSI technology. The application domain of the devised techniques is radio frequency identification (RFID) systems, however the presented techniques are applicable to wide range of mixed mode analog-digital applications. Hence the techniques herein apply to a range of smart wireless or mobile systems. The integration of both analog and digital circuits on a single substrate has many benefits such as reducing the system power, increasing the system reliability, reducing the system size and providing high inter-system communications speed – hence, a cost effective system implementation with increased performance. On the other hand, some difficulties arise from the fact that standard low-cost CMOS technologies are *tuned* toward maximising digital circuit performance and increasing transistor density per unit area. Usually these technologies have a wide spread in transistor parameters that require new design techniques that provide circuit characteristics based on relative transistor parameters rather than on the absolute value of these parameters.

This research has identified new design techniques for mostly analog and some digital circuits for implementation in standard CMOS technologies with design parameters dependent on the relative values of process parameters, resulting in technology independent circuit design techniques. The techniques presented and discussed in this dissertation are (i) applied to the design of low-voltage and low-power controlled gain amplifiers, (ii) digital trimming techniques for operational amplifiers, (iii) low-power and low-voltage Schmitt trigger circuits, (iv) very low frequency to medium frequency low power oscillators, (v) low power Gray code counters, (vi) analog circuits utilising the neuron MOS transistor, (vii) high value floating resistors, and (viii) low power application specific integrated circuits (ASICs) that are particularly needed in radio frequency identification systems. The new techniques are analysed, simulated and verified experimentally via five chips fabricated through the MOSIS service.

This page is blank

# **Declaration**

This work contains no material which has been accepted for the award of any other degree or diploma in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text.

I give consent to this copy of the thesis, when deposited in the University Library, being available for loan and photocopying.

Signed : \_\_\_\_\_ Date : 14<sup>th</sup> February, 2003

This page is blank

0.0

# Publications

## **Patents**

- [1] S.F. Al-Sarawi, "A current controlled very high value floating CMOS resistor," Australian Patent Office, Application No. PR 7389, September 2001.

- [2] P. Celinski, S.F. Al-Sarawi, and D. Abbott, "A level sensitive latch," Australian Patent Office, Application No. PR 2230, December 2000.

## **Book Chapters**

- [1] S.F. Al-Sarawi and T. Sarros, *Handbook of Smart Structures and MEMS*, "Optoelectronic A/D conversion," IOP, UK, 2003, accepted.

- [2] S.F. Al-Sarawi and D. Abbott, *Handbook of Smart Structures and MEMS*, "Three dimensional IC packaging," IOP, UK, 2003, accepted.

- [3] P. Celinski, S. Al-Sarawi, D. Abbott, and J.F. Lopez, Advances in Systems Theory, Mathematical Methods and Applications, "A family of low depth threshold logic, carry lookahead adders," WSEAS Press, 2002, ISBN 960-8052-61-0, Invited.

- [4] P. Celinski, J.F. Lopez, S. Al-Sarawi, and D. Abbott, Advances in Systems Theory, Mathematical Methods and Applications, "A compact (m,n) parallel counter circuit based on self timed threshold logic," WSEAS Press, 2002, ISBN 960-8052-61-0, Invited.

- [5] P. Celinski, T. Townsend, S. Al-Sarawi, D. Abbott, and J.F. Lopez, Advances in Systems Theory, Mathematical Methods and Applications, "A compact parallel multiplication scheme based on (7,3) and (15,4) self-timed threshold logic counters," WSEAS Press, 2002, ISBN 960-8052-61-0, Invited.

## **Journal Papers**

- L. Lee, S.F. Al-Sarawi, and D. Abbott, "A low power shift register," *Electronics Letters* (IEE), Vol. 39, no. 1, pp. 19–20, January 2003.

- S.F. Al-Sarawi, "A novel topology for grounded-to-floating resistor conversion in CMOS technology," *Microelectronics Journal* (Elsevier), Vol. 33, no. 12, pp. 1059– 69, December 2002.

- [3] S.F. Al-Sarawi, "Low power schmitt trigger circuit," *Electronics Letters* (IEE), Vol. 38, no. 18, pp. 1009–10, August 2002.

- [4] P. Celinski, J.F. López, S. Al-Sarawi, and D. Abbott, "A compact (m,n) parallel counter circuit based on self timed threshold logic," *Electronics Letters* (IEE), Vol. 38, no. 13, pp. 633-5, June 2002.

- [5] S.F. Al-Sarawi, P.B. Atanackovic, W. Marwood, B.A. Clare, K.A. Corbett, K.J. Grant, and J. Munch, "Differential oversampling data converters in SEED technology," *Microelectronics Journal* (Elsevier), Vol. 33, pp. 141–51, January 2002.

- [6] P. Celinski, J.F. Lopez, S.F. Al-Sarawi, and D. Abbott, "Low power, high speed, charge recycling CMOS threshold logic gate," *Electronics Letters* (IEE), Vol. 37, no. 17, pp. 1067–9, August 2001.

- [7] S.F. Al-Sarawi, N. Burgess, W. Marwood, Atanackovic, and D. Abbott, "Very high speed differential optoelectronic algorithmic ADC using n-i(MQW)-n SEED technology," *Microelectronics Journal* (Elsevier), Vol. 31, no. 7, pp. 593–604, August 2000.

- [8] P. Celinski, D. Abbott, S.F. Al-Sarawi, and J.F. López, "Novel extension of neu-MOS techniques to neu-GaAs," *Microelectronics Journal* (Elsevier), Vol. 31, no. 7, pp. 577–82, 2000.

- [9] P. Celinski, J.F. López, S.F. Al-Sarawi, and D. Abbott, "A complementary neu-GaAs structure," *Electronics Letters* (IEE), Vol. 36, no. 5, pp. 424–5, March 2000.

- [10] S.F. Al-Sarawi, D. Abbott, and P. Franzon, "A review of 3-D packaging technology," *IEEE Transactions on Components, Packaging and Manufacturing Technology Part B: Advanced Packaging*, Vol. 20, no. 1, pp. 2–14, February 1998.

## **Conference Papers**

- S.F. Al-Sarawi, "New efficient offset voltage cancellation techniques using digital trimming," in *Proc. of SPIE VLSI Circuits and Systems*, Canary Islands, Spain, May 2003, accepted.

- [2] Y. Zhu, S.F. Al-Sarawi, and M. Liebelt, "A differential 6th order continuous time bandpass sigma delta modulator in CMOS technology," in *Proc. of SPIE VLSI Circuits and Systems*, Canary Islands, Spain, May 2003, accepted.

- [3] L. Ricciardi, S.F. Al-Sarawi, I. Pitz, V. Varadan, and D. Abbott, "Investigation into the future of RFID in biomedical applications," in *Proc. of SPIE VLSI Circuits* and Systems, Canary Islands, Spain, May 2003, accepted.

- [4] P. Celinski, J.F. Lopez, S.F. Al-Sarawi, and D. Abbott, "A family of low depth, threshold logic, carry lookahead adders," in *Proc. of 2nd WSEAS International* conference on instrumentation, measurement, control, circuits and systems, Mexico, May 2002, pp. 1981–3.

- [5] L. Lee, S. Al-Sarawi, and D. Abbott, "Low-power serial-to-parallel dynamic shift register," in *Proc. SPIE Smart Structures, Devices, and Systems*, Melbourne, Australia, December 2002, Vol. 4935, pp. 188–96.

- [6] Y. Zhu, M. Leibelt, and S. Al-Sarawi, "Variable center frequency bandpass sigmdelta modulator in SOS CMOS technology," in *Proc. SPIE Smart Structures, De*vices, and Systems, Melbourne, Australia, December 2002, Vol. 4935, pp. 197–204.

- [7] I. Pitz, L. Hall, H. Hansen, V. Varadan, C. Bertram, S. Maddocks, S. Enderling, D. Saint, S. Al-Sarawi, and D. Abbott, "Trade-offs for wireless communication in biotelemetric applications," in *Proc. SPIE Biomedical Applications of Micro- and Nanoengineering*, Melbourne, Australia, December 2002, Vol. 4937, pp. 307–18.

- [8] T. Sarros, S. Al-Sarawi, K. Corbett, K. Grant, B. Clare, and W. Marwood, "Oversampled optoelectronic analog-to-digital converters using sigma-delta modulation," in *Proc. SPIE Smart Structures, Devices, and Systems*, Melbourne, Australia, December 2002, Vol. 4935, pp. 178–87.

- [9] S.F. Al-Sarawi, "A new current controlled very high value floating CMOS resistor," in Proc. SPIE Electronics and Structures for MEMS II, Adelaide, South Australia, December 2001, Vol. 4591, pp. 231–40.

#### **CONFERENCE PAPERS**

- [10] P. Celinski, J.F. Lopez, S.F. Al-Sarawi, and D. Abbott, "Low power, high speed threshold logic and its application to the design of novel carry lookahead adders," in *Proc. SPIE Electronics and Structures for MEMS II*, Adelaide, South Australia, December 2001, Vol. 4591, pp. 258–65.

- [11] S.F. Al-Sarawi, "A very high value floating CMOS resistor," in 9th International Symposium on Integrated Circuits, Devices & Systems, Singapore, September 2001, pp. 370-3.

- [12] S.F. Al-Sarawi, "Analog circuits using neuron MOS transistor," in 9th International Symposium on Integrated Circuits, Devices & Systems, Singapore, September 2001, pp. 366-9.

- [13] P. Ryan, T. Arivoli, L. De-Souza, G. Foyster, R. Keaney, T. McDermott, A. Moini, S. Al-Sarawi, L. Parker, G. Smith, N. Weste, and G. Zyner, "A single chip PHY COFDM modem for IEEE 802.11a with integrated ADCs and DACs," in *IEEE International Solid-State Circuits Conference – ISSCC*, San Francisco, CA, February 2001, pp. 338–9.

- [14] P. Celinski, S.F. Al-Sarawi, and D. Abbott, "Delay analysis of neuron-MOS and capacitive threshold logic," in *Proc. of the 7th IEEE International Conference on Electronics, Circuits and Systems*, Jounieh, Lebanon, December 2000, pp. 932–5.

- [15] S.F. Al-Sarawi, W. Marwood, D. Abbott, and Atanackovic, "An integrated optoelectronic oversampling analog-to-digital converter," in *Proc. SPIE Smart Electronics* and MEMS II, Melbourne, Australia, December 2000, Vol. 4236, pp. 351–60.

- [16] S.F. Al-Sarawi, N. Burgess, W. Marwood, and Atanackovic, "Very high speed differential optoelectronic algorithmic ADC using n-i(MQW)-n SEED technology," in *Proc. SPIE Design, Characterization, and Packaging for MEMS and Microelectronics*, Queensland, Australia, October 1999, Vol. 3893, pp. 248–295.

- [17] W. Marwood, P. Atanackovic, J. Munch, N. Burgess, and S.F. Al-Sarawi, "A MMIC compatible photonic A/D converter," in *Third International Conference on* Advanced A/D and D/A Conversion Techniques and their Applications, Glasgow, UK, July 1999, pp. 17–20.

- [18] B. Gonzalez, D. Abbott, S.F. Al-Sarawi, A. Hernandez, J. Garcia, and J. López, "Efficient transistor count reduction for a low power GaAs A/D converter," in

Proc. XIII Design of Circuits and Integrated Systems Conf. (DCIS'98), Madrid, Spain, November 1998, pp. 62–6.

- [19] D. Abbott, S.F. Al-Sarawi, B. Gonzalez, J. López, J. Austin-Crowe, and K. Eshraghian, "Neu-MOS (νMOS) for smart sensors and extension to a novel neu-GaAs (νGaAs) paradigm," in Proc. of IEEE International Conference on Electronics, Circuits & Systems, Lisbon, Portugal, September 1998, pp. 397–404, Invited.

- [20] D. Abbott, S.F. Al-Sarawi, and P. Franzon, "3D packaging technology for portable systems," in *Proc. 14th IREE Australian Microelectronics Conference*, Melbourne, October 1997, pp. 221–6, Invited.

- [21] S.F. Al-Sarawi, P.H. Cole, and D. Abbott, "Very low frequency low power oscillators," in *Proc. 14th IREE Australian Microelectronics Conference*, Melbourne, October 1997, pp. 46–50.

- [22] S.F. Al-Sarawi, D. Abbott, and P.H. Cole, "Application of neuron MOS in analog design," in *Proc. 14th IREE Australian Microelectronics Conference*, Melbourne, October 1997, pp. 123–8.

- [23] S.F. Al-Sarawi and P.H. Cole, "Digital trimming for operational amplifiers," in Proc. 13th IREE Australian Microelectronics Conference, Adelaide, July 1995, pp. 322-7.

- [24] P.H. Cole and S.F. Al-Sarawi, "A low power ripple through Gray code counter," in Proc. 13th IREE Australian Microelectronics Conference, Adelaide, July 1995, pp. 175-9.

- [25] P.H. Cole and S.F. Al-Sarawi, "Three new controlled gain amplifier circuits," in Proc. 12th IREE Australian Microelectronics Conference, Gold Coast, October 1993, pp. 141–6.

- [26] S.F. Al-Sarawi and P.H. Cole, "Three new Schmitt trigger circuits with adjustable hysteresis," in *Proc. 12th IREE Australian Microelectronics Conference*, Gold Coast, Australia, October 1993, pp. 141–6.

- [27] S.F. Al-Sarawi, "Design techniques for ultra low power circuits," in Proc. of SUPRA PWP Conference, Sydney, Australia, October 1991, pp. 70–82, Sydney University.

This page is blank

# Acknowledgement

I would like to thank my supervisor Assoc. Prof. Derek Abbott for providing boundless enthusiasm and encouragement during this research. I also would like to thank Prof. Peter Cole and the directors and staff members of Integrated Silicon Design Pty. Ltd. for sponsoring this research and providing help when needed. Special thanks to Mr. Alf Grasso, Mr. Leigh Turner, Mr. Michael Loukine and Miss Susan Wu for lots of fruitful discussions especially in the early stages of this research.

I also would like to thank the academic, technical, secretarial staff members in the department for providing lots of help and support, the CHiPTec Group and the Tea Club members in the School of Electrical and Electronic Engineering. Special thanks to Dr. Cheng-Chew Lim, Mr. Mike Liebelt, Dr. Andrew Beaumont-Smith, Prof. Neil Burgess, Dr. Ali Moini, Dr. Richard Beare, Dr. Andy Blanksby, Dr. Ken Sarkies, Mr. Kiet To, Dr. Andrew Parfitt, Dr. Shannon Morton, Dr. Sam Appleton, Dr. Chris Howland, and Mr. Angelo Iannella for their support and encouragement. The supervisory input of Prof. Peter Cole, Dr. Ali Moini and Dr. Cheng-Chew Lim at various stages of this project is acknowledged, as well as the initial vision of Prof. Peter Cole that drove the earlier phase of this project. I also extend my thanks to the VLSI and Vision groups in the department for allowing me to use their resources. I also would like to thank Mr. David Bowler and Mr. Kiet To for being very helpful with setting up CAD tools and providing help with LATEXproblems, and Mr. David Pawsey for his encouragement, advice, and support in the early stages of my settlement in Adelaide.

I would like to acknowledge and thank Mr. David Hall and Dr. David Murfett for conducting the preliminary test on the digitally trimmed circuit and spending the time and effort to understand the circuit. I also would like to thank Mr. Greg Pope from Integrated Silicon Design for providing the measurement results for the program mode detection circuit. Furthermore, I extend my thanks to Mr. Kelvin Tan for putting in the effort and preparing a PCB for testing the neuron MOS circuits and reporting some of the results as part of his final year project. Also I would like to thank Mr. Peter Celinski

#### Acknowledgement

for lots of useful interaction and discussion and for carrying further research into the area of neuron MOS technology.

For the section on 3D-VLSI technology I would like to thank Dr. Andre Yakovleff and Dr. Paul Miller, of LSOD, DSTO, Australia for many constructive manuscript comments. Useful discussions with Christian Val, 3D Plus, France; Leon Arndt and William Shroeder, Raytheon, Tewksbury, MA; Bruce Totty and Douglas Pongrance, Irvine Sensors, Costa Mesa, CA; Rob Terrill and Gary Beene, Texas Instruments, Dallas, TX; Ed Palmer, Harris Corp, Melbourne, FL; are gratefully acknowledged.

I would like to acknowledge funding from the School of Electrical and Electronic Engineering at Adelaide University, Australian Research Council (ARC), Defence Science and Technology Organisation (DSTO) and Integrated Silicon Design Pty. Ltd. that have supported me at various phases of this PhD program.

I would like to thank my wife Najwa and my children for their patience, support and putting up with the long hours of study and work, and my in-law family and my friends for continuous encouragement and support. Last, but not least, I would like to express my gratitude and thanks to my Mum, Dad, sister and brothers for continuing support and encouragement all the years.

| 1.1  | Voltage headroom for various analog circuits modules                                        | 7  |

|------|---------------------------------------------------------------------------------------------|----|

| 2.1  | Digital inverter used as a push-pull amplifier.                                             | 27 |

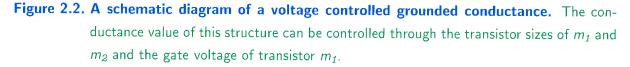

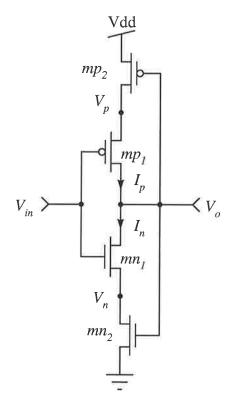

| 2.2  | A schematic diagram of a voltage controlled grounded conductance                            | 28 |

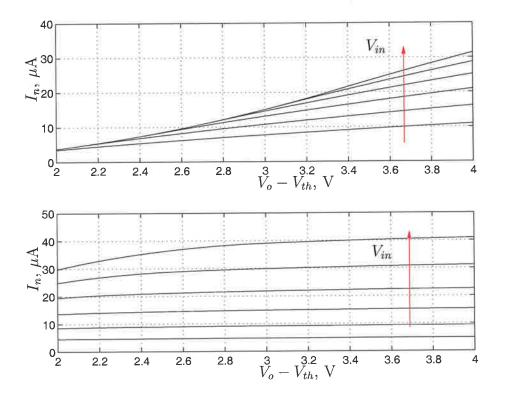

| 2.3  | The simulation results of the grounded resistor.                                            | 29 |

| 2.4  | A controlled gain amplifier which uses a series transistor configuration (STC).             | 30 |

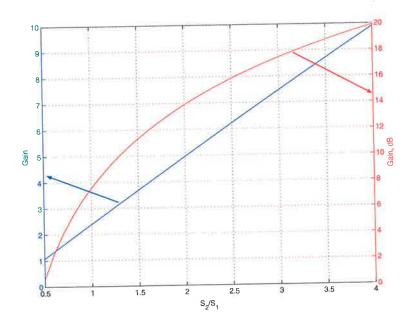

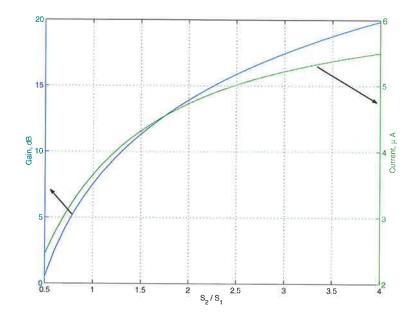

| 2.5  | DC simulation results of the series transistor configuration amplifier                      | 31 |

| 2.6  | DC simulation results of current drawn from the supply rail for the con-                    |    |

|      | trolled gain amplifier as function of transistor ratios.                                    | 32 |

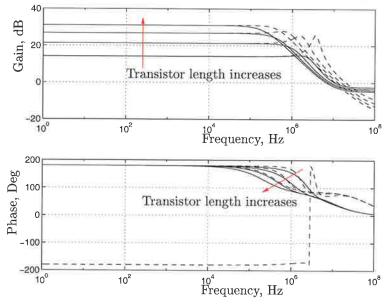

| 2.7  | AC simulation results of the STC amplifier.                                                 | 33 |

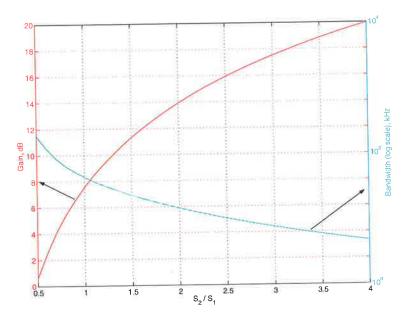

| 2.8  | Simulation results of the STC amplifier using Taiwan Semiconductor Man-                     |    |

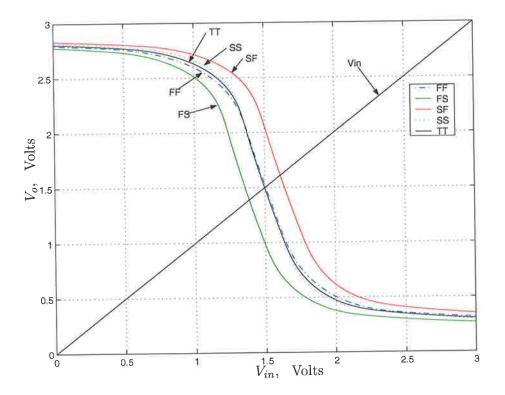

|      | ufacturing Company (TSMC) skew parameters.                                                  | 34 |

| 2.9  | Simulation results of the STC amplifier as function of temperature                          | 35 |

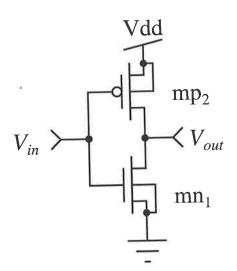

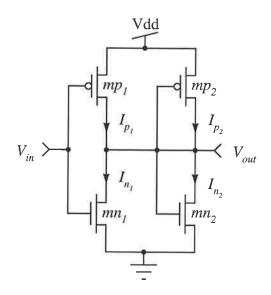

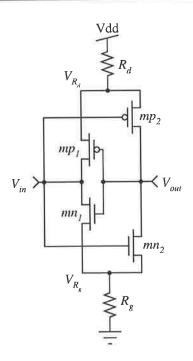

| 2.10 | A parallel transistor configuration (PTC) controlled gain amplifier. $\ldots$               | 36 |

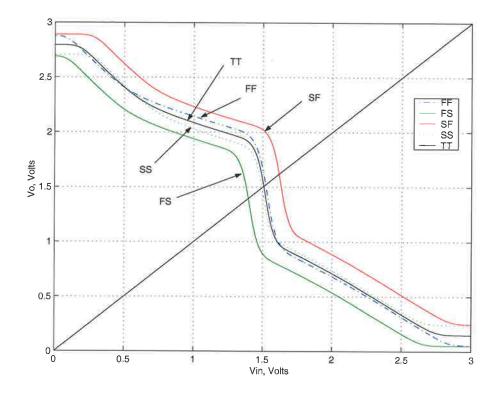

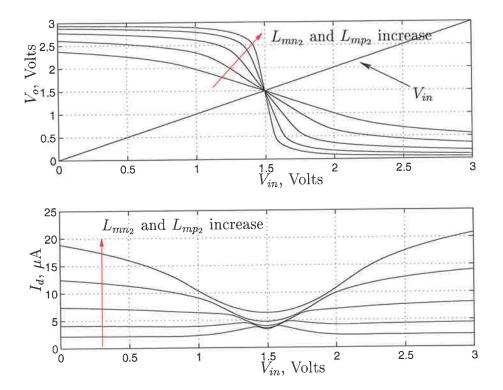

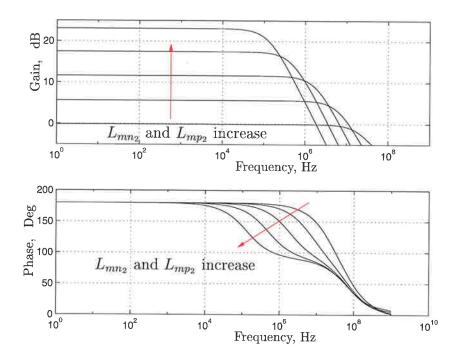

| 2.11 | Simulation results of the PTC amplifier.                                                    | 37 |

| 2.12 | Frequency response of the PTC amplifier                                                     | 38 |

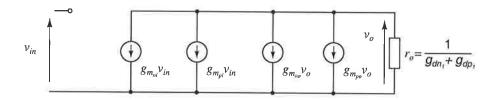

| 2.13 | Small signal equivalent circuit of the PTC amplifier                                        | 38 |

| 2.14 | Simulation results of the PTC amplifier using the TSMC skew parameters.                     | 39 |

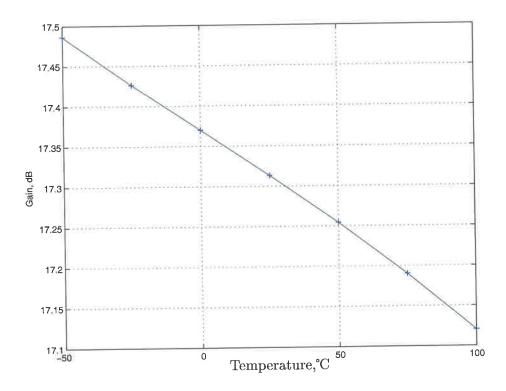

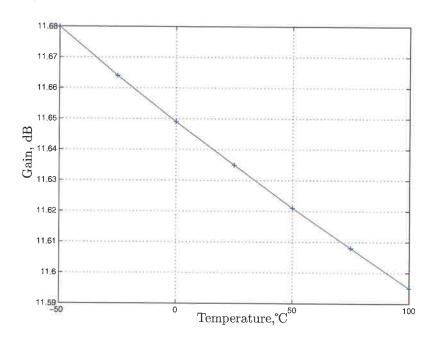

| 2.15 | Simulation results of the PTC amplifier as function of temperature. The                     |    |

|      | temperature was varied from -50 to 100 °C in 25 °C step                                     | 40 |

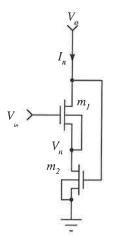

| 2.16 | A current mirrors configuration (CMC) controlled gain amplifier amplifier.                  | 41 |

| 2.17 | DC simulation results of the CMC amplifier.                                                 | 42 |

| 2.18 | Frequency response of the CMC amplifier.                                                    | 42 |

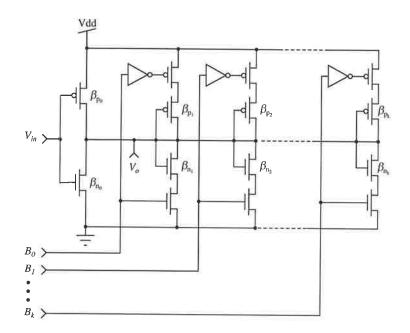

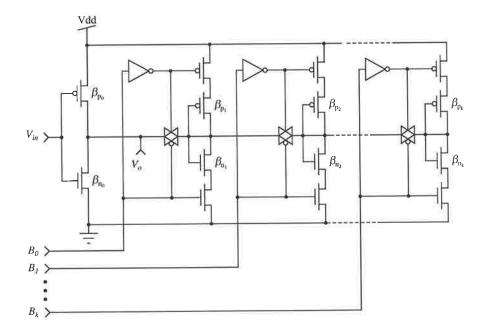

| 2.19 | A schematic diagram of a digital soft-hardware controlled gain amplifier. $% \mathcal{A}$ . | 44 |

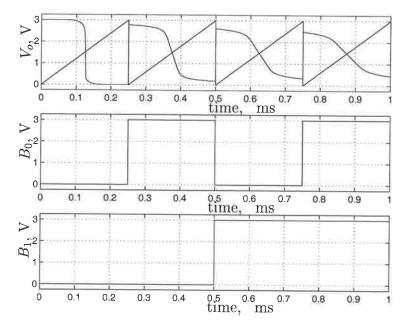

| 2.20 | Simulation results of the digitally programmable controlled gain amplifier.                 | 44 |

| 2.21 | A schematic diagram of a digital soft-hardware controlled gain amplifier                    |    |

|      | with less load capacitance                                                                  | 45 |

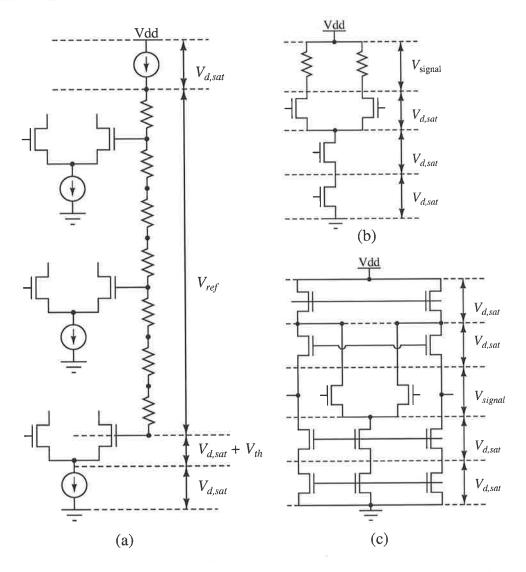

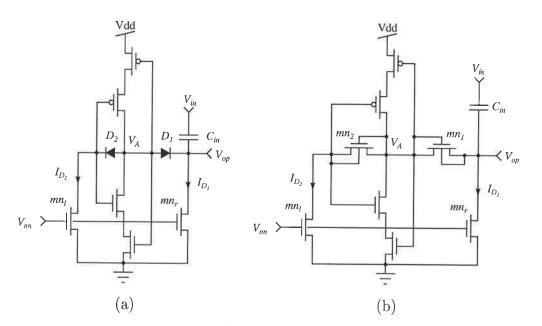

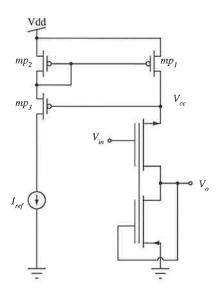

| 2.22 | Biasing circuits for the STC amplifier.                                                     | 46 |

|      |                                                                                             |    |

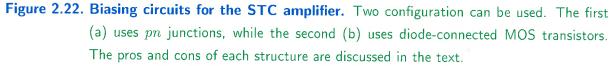

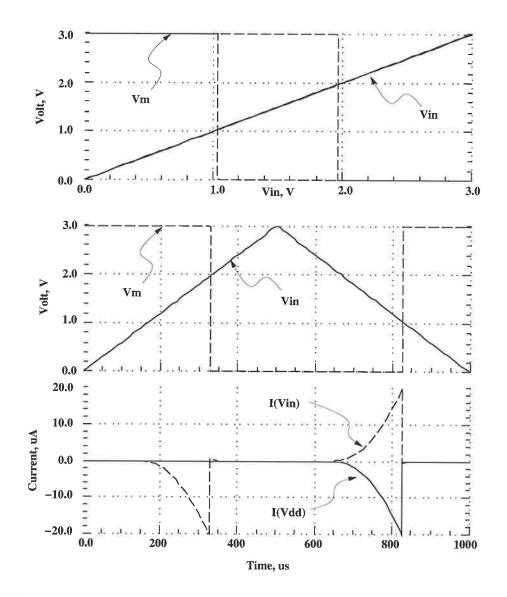

| 2.23 | Simulation results of the $pn$ and MOS transistors STC biasing circuits                          | 47 |

|------|--------------------------------------------------------------------------------------------------|----|

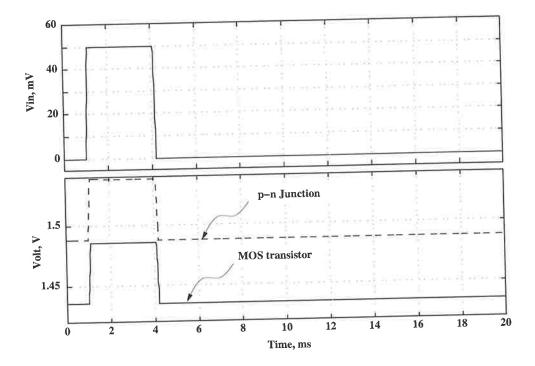

| 2.24 | The schematic diagram of the fabricated $pn$ junction STC bias and STC                           |    |

|      | amplifier circuits.                                                                              | 49 |

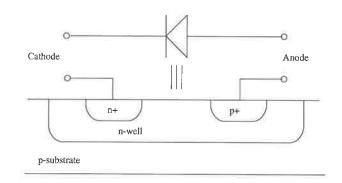

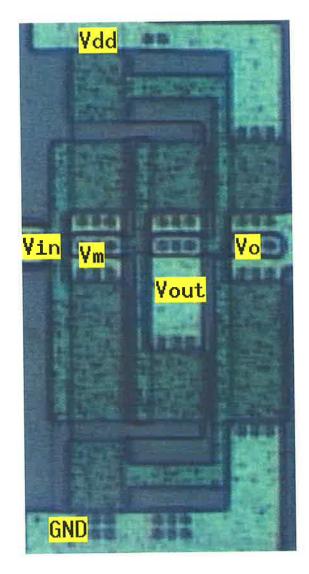

| 2.25 | A implemented in an n-well process                                                               | 50 |

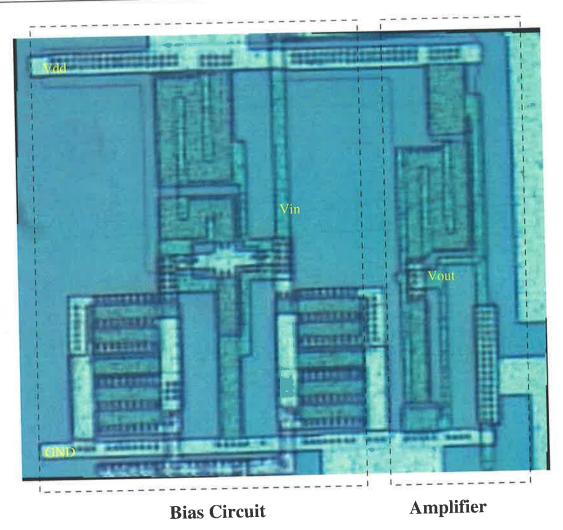

| 2.26 | A micro-photograph of the fabricated STC amplifier.                                              | 51 |

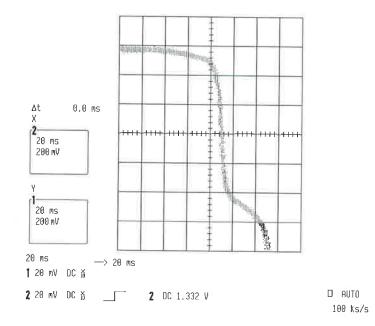

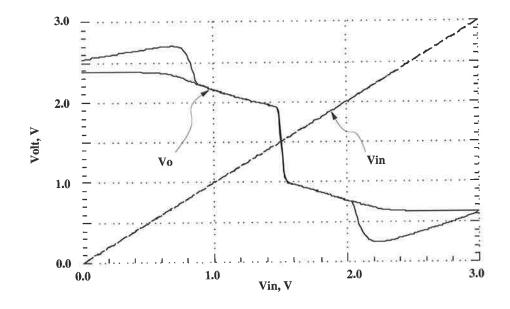

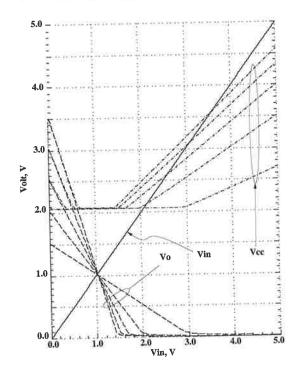

| 2.27 | Measured input-output characteristics of the STC amplifier at 3 Volt supply.                     | 52 |

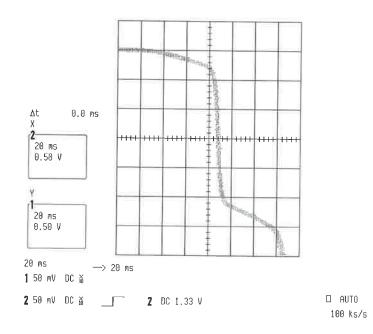

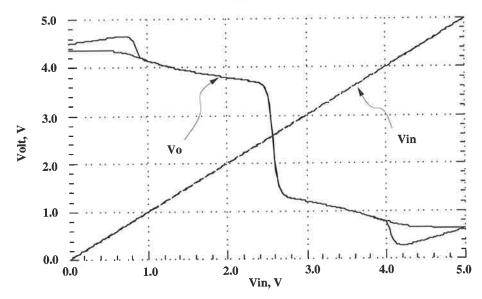

| 2.28 | Measured input-output characteristics of the STC amplifier at 5 Volt supply.                     |    |

| 2.29 | The simulation results of the fabricated STC amplifier at 3 Volt supply                          | 53 |

| 2.30 | Simulation results of the fabricated STC amplifier at 5 Volt supply.                             | 53 |

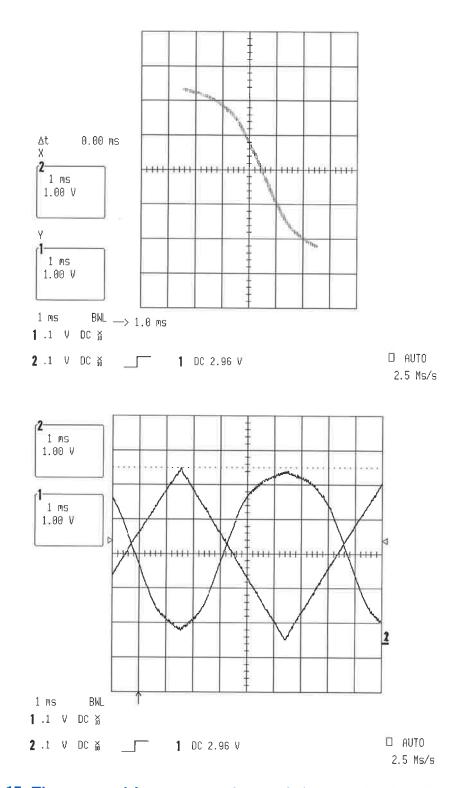

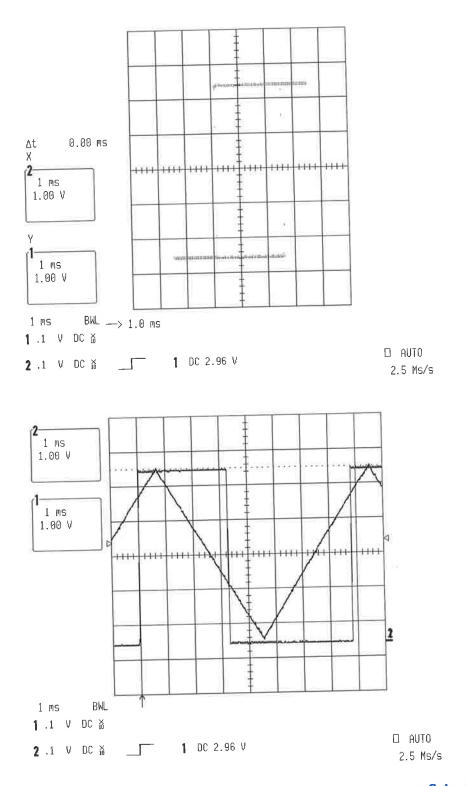

| 2.31 | Measured characteristics of the unity gain PTC amplifier                                         |    |

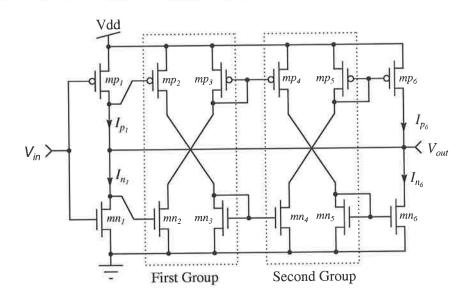

| 2.32 | Circuit diagram of the implemented PTC amplifier with 6 dB gain                                  |    |

| 2.33 | Measured input-output characteristics of the 6 dB gain PTC amplifier. $\therefore$               |    |

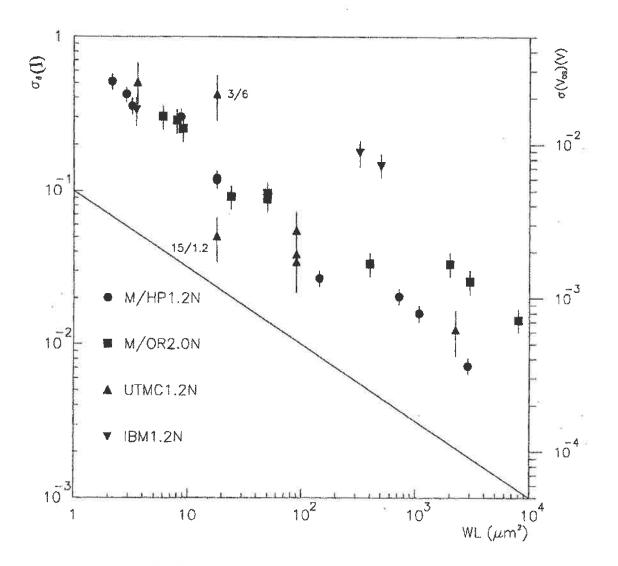

| 3.1  | Current and voltage mismatch versus drawn device area.                                           |    |

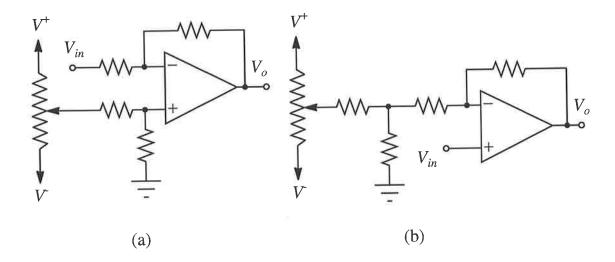

| 3.2  | Two common techniques for offset voltage compensation.                                           | 67 |

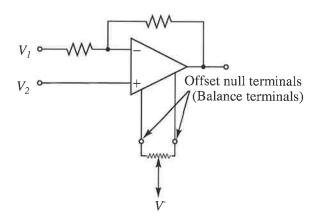

| 3.3  | Offset voltage compensation using null terminals.                                                |    |

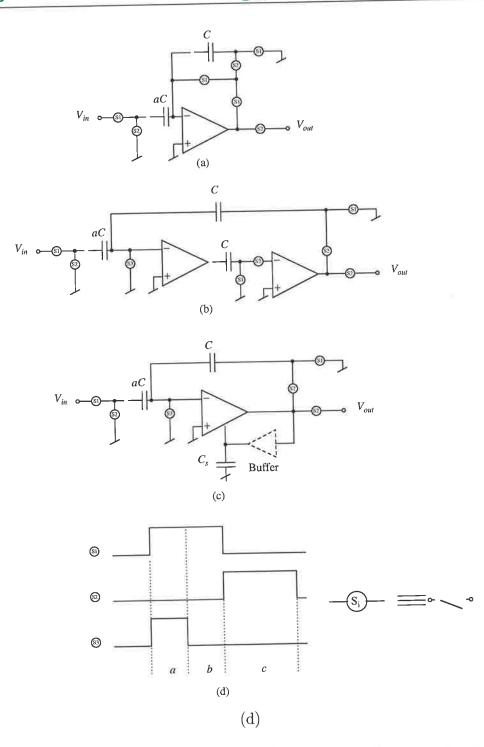

| 3.4  | Auto-zero cancellation techniques.                                                               | 69 |

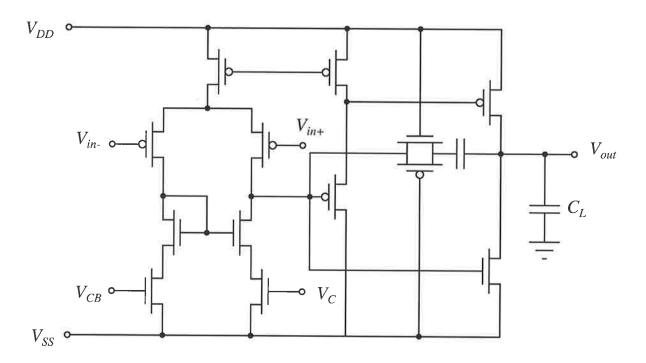

| 3.5  | Offset adjustable two stage CMOS op-amp using a programmable current                             |    |

|      | mirror                                                                                           | 70 |

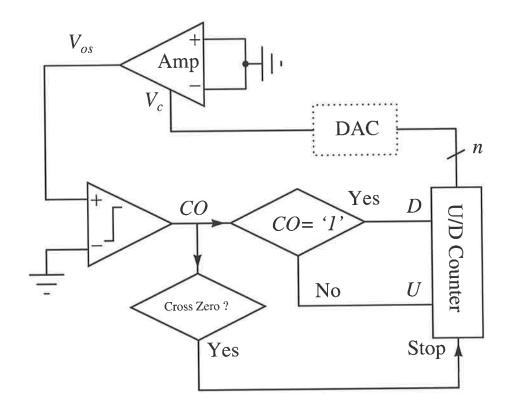

| 3.6  | Concept of the offset tuning scheme.                                                             | 71 |

| 3.7  | A single ended voltage comparator trimmed using a weighted-voltage trim-                         |    |

|      | ming technique.                                                                                  | 72 |

| 3.8  | A digitally trimmed differential amplifier using the weighted-voltage tech-                      |    |

|      | nique. $\ldots$ | 73 |

| 3.9  | A digitally trimmed differential amplifier with extended common mode                             |    |

|      | range using a weighted voltage technique                                                         | 74 |

| 3.10 | A digitally trimmed differential amplifier with extended common mode                             |    |

|      |                                                                                                  | 77 |

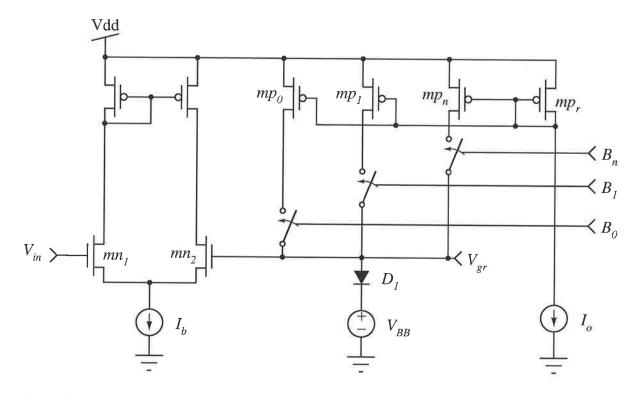

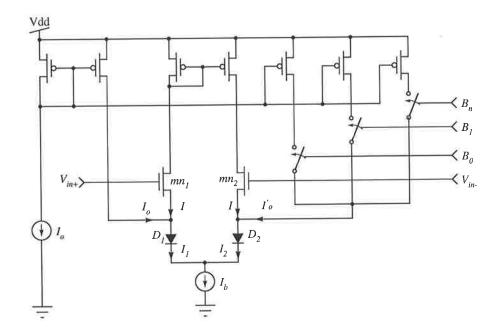

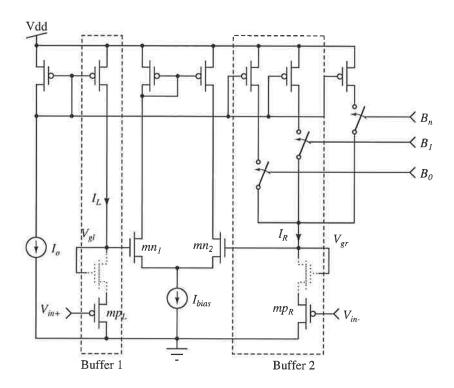

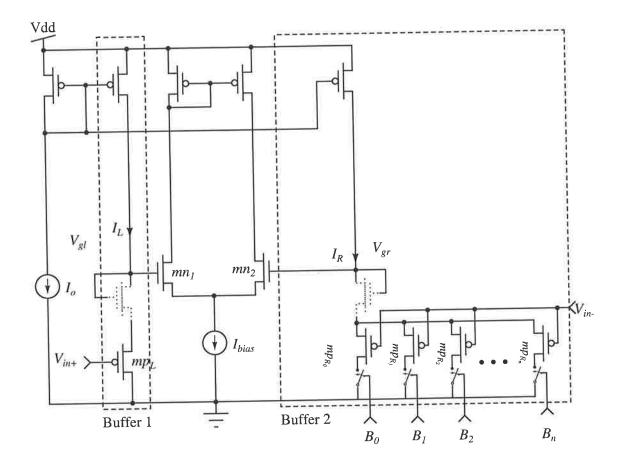

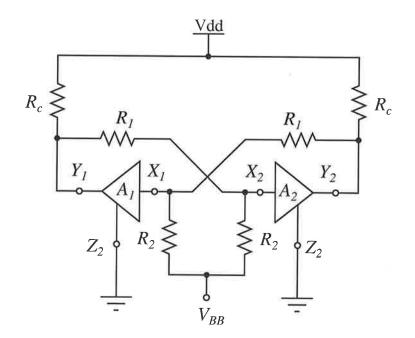

| 3.11 | A digitally trimmed differential amplifier using a weighted-current technique.                   | 78 |

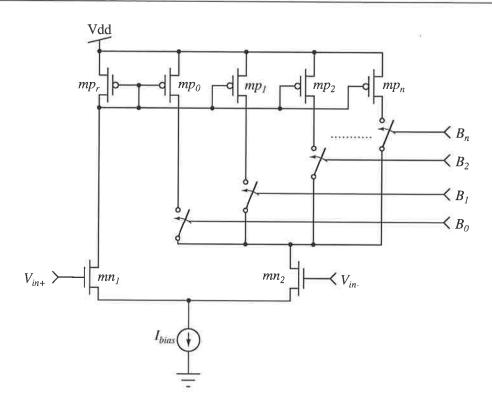

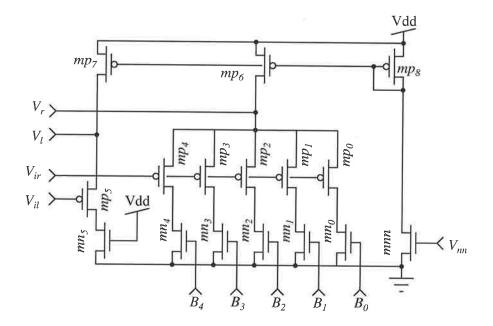

| 3.12 | A schematic diagram of the digitally programmable arms                                           | 80 |

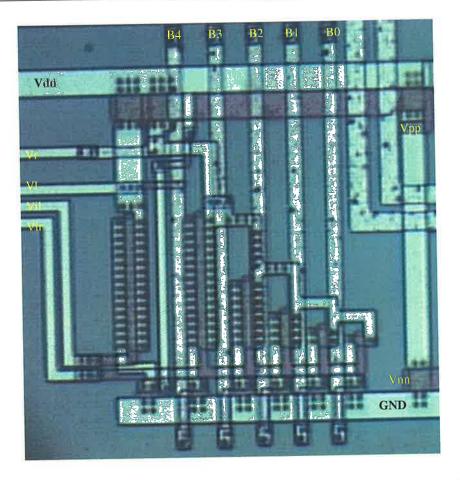

| 3.13 | A micro-photograph of the fabricated of the digitally programmable trim-                         |    |

|      |                                                                                                  | 81 |

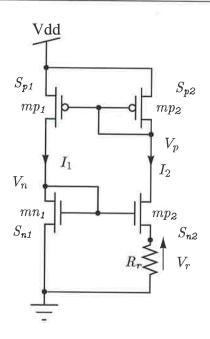

| 3.14 | The bandgap voltage reference circuit.                                                           | 82 |

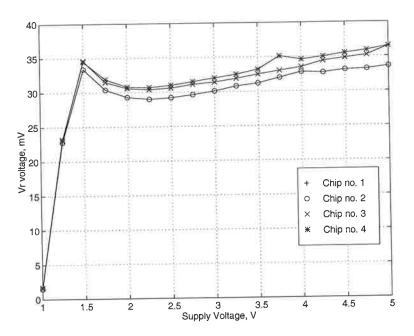

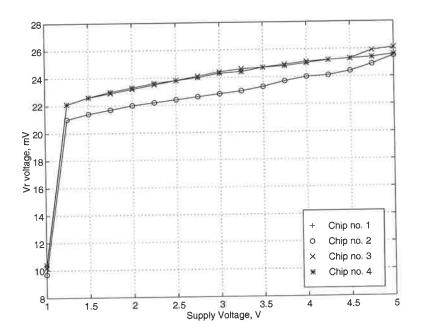

| 3.15 | Measurements of the bandgap voltage reference circuit as function of the                         |    |

|      | supply voltage using 100 k $\Omega$ resistor.                                                    | 83 |

| 3.16 | Measurements of the bandgap voltage reference circuit as function of the supply voltage using a 1 M $\Omega$ resistor |

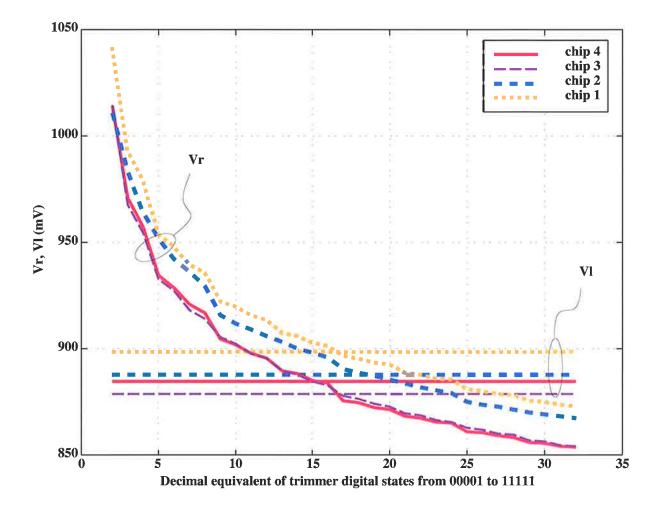

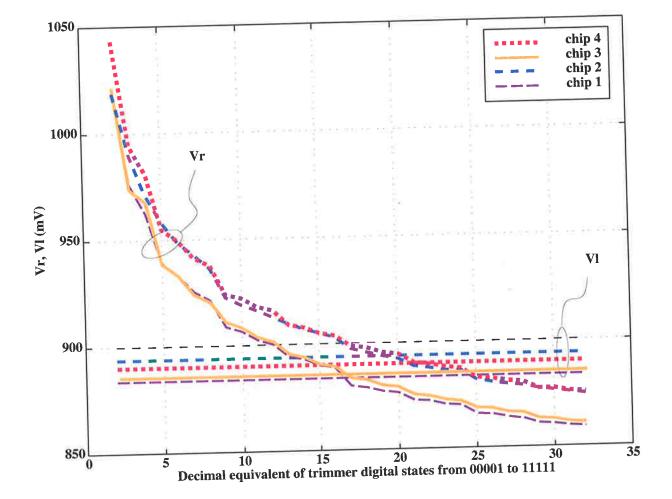

|------|-----------------------------------------------------------------------------------------------------------------------|

| 3.17 | Measured voltage difference between the trimmer's arms as function of the state of digitally programmable switches    |

| 3.18 | Measured voltage difference between the trimmer's arms as function of the state of digitally programmable switches    |

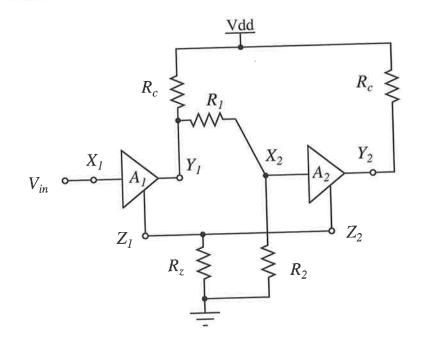

| 4.1  | A binary circuit with two amplifying devices $A_1$ and $A_2$                                                          |

| 4.2  | A Schmitt trigger circuit based on the binary circuit shown in Figure 4.1 $95$                                        |

| 4.3  | A conceptual Schmitt trigger circuit with large hysteresis in bipolar tech-                                           |

|      | nology                                                                                                                |

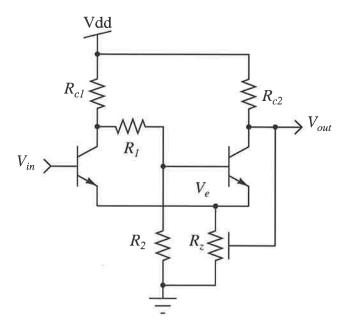

| 4.4  | A wide hysteresis CMOS Schmitt trigger derived from the bipolar version. 99                                           |

| 4.5  | A simplified Schmitt trigger circuit with its input signal is low 99                                                  |

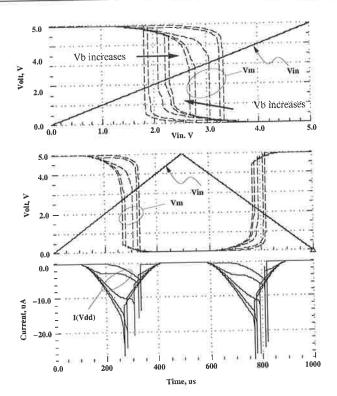

| 4.6  | Simulation results of the Schmitt trigger circuit shown in Figure 4.4 101                                             |

| 4.7  | A pMOS Schmitt trigger derived from the nMOS Schmitt trigger circuit                                                  |

|      | shown in Figure 4.4                                                                                                   |

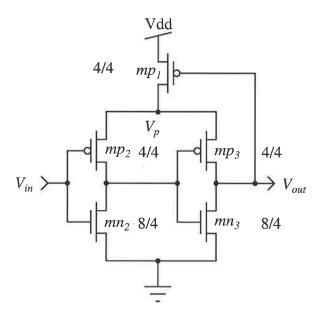

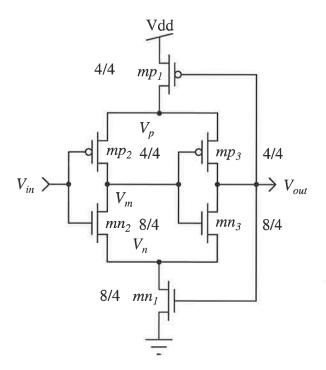

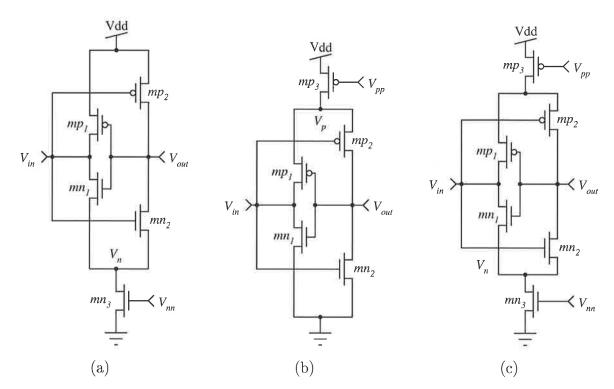

| 4.8  | A new CMOS Schmitt trigger circuit                                                                                    |

| 4.9  | Simulation results of the complementary Schmitt trigger circuit shown in                                              |

|      | Figure 4.8                                                                                                            |

| 4.10 | An nMOS and pMOS complementary voltage controlled grounded resistors. 105                                             |

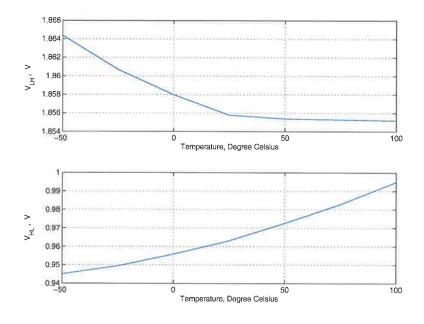

| 4.11 | Temperature simulation results of the low power Schmitt trigger circuits 106                                          |

| 4.12 | Three approaches to adjust the hysteresis width of the Schmitt trigger                                                |

|      | circuit shown in Figure 4.8                                                                                           |

| 4.13 | Simulation results of the adjustable hysteresis Schmitt trigger circuit shown                                         |

|      | in Figure 4.12.b                                                                                                      |

| 4.14 | Simulation results of the adjustable hysteresis Schmitt trigger circuit shown                                         |

|      | in Figure 4.12.c                                                                                                      |

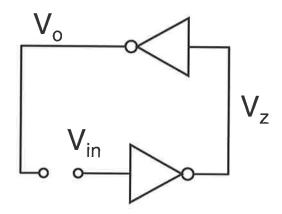

| 4.15 | A CMOS bistable circuit                                                                                               |

| 4.16 | The simulated input-output characteristics of the bistable circuit shown                                              |

|      | in 4.15                                                                                                               |

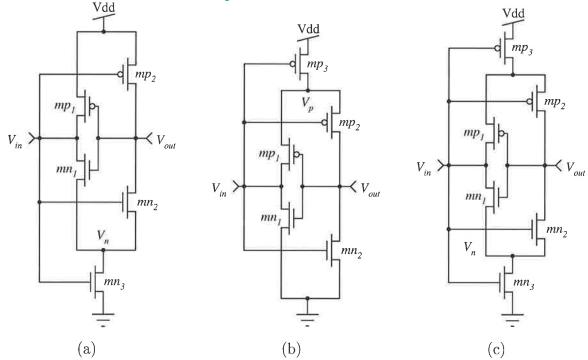

| 4.17 | A schematic diagram of the finite input impedance Schmitt trigger circuit. 112                                        |

| 4.18 | A simplified circuit a schematic diagram of the finite input impedance                                                |

|      | Schmitt trigger circuit                                                                                               |

| 4.19 | Simulation results of the Schmitt trigger circuit shown in Figure 4.17 114                                            |

| 4.20 | A schematic diagram of a fully symmetrical Schmitt trigger circuit with a                                             |

|      | finite input impedance                                                                                                |

ł

| 4.21 | Simulation results of the Schmitt trigger circuit shown in Figure 4.20 116                                                                                                   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.22 | Simulation results of the Schmitt trigger circuit shown in Figure 4.23.c 117                                                                                                 |

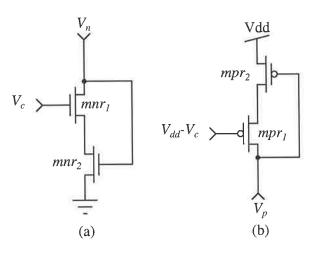

| 4.23 | Three finite input impedance Schmitt trigger circuits                                                                                                                        |

| 4.24 | Three self-biased finite input impedance Schmitt trigger circuits 118                                                                                                        |

| 4.25 | Simulation results of the self-biased Schmitt trigger circuit shown in Fig-                                                                                                  |

|      | ure 4.24.c                                                                                                                                                                   |

| 4.26 | A micro-photograph of the fabricated Schmitt trigger circuit shown in Fig-                                                                                                   |

|      | ure 4.8                                                                                                                                                                      |

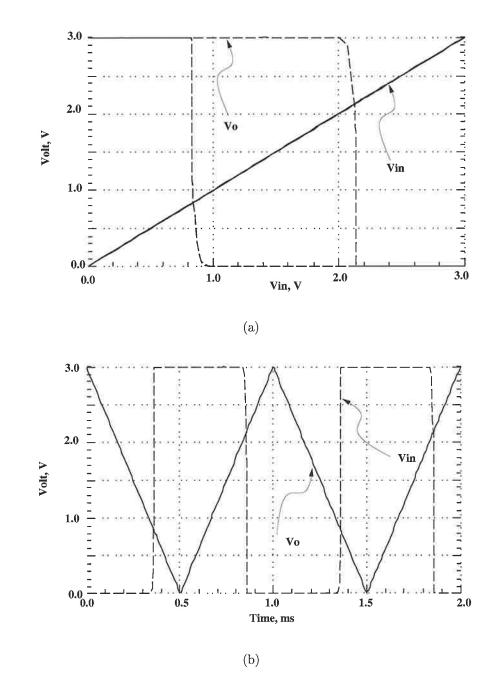

| 4.27 | Simulation results of the fabricated Schmitt trigger circuit at 3 V 122                                                                                                      |

| 4.28 | Simulation results of the fabricated Schmitt trigger circuit at 5 V 123                                                                                                      |

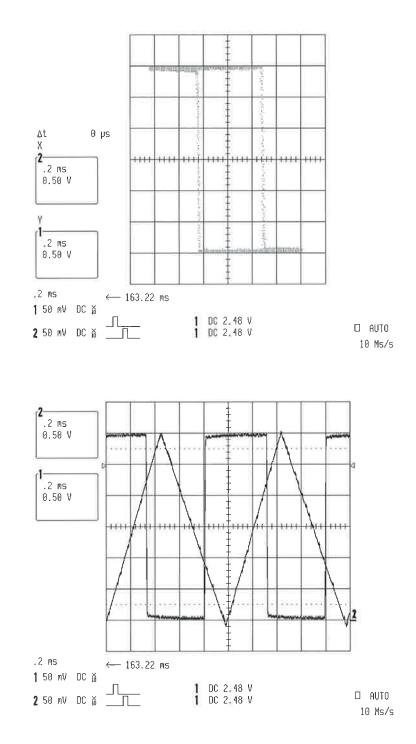

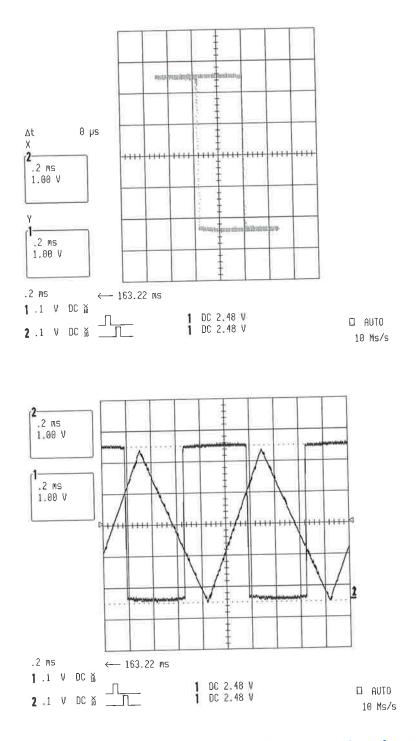

| 4.29 | Measured characteristics of the fabricated Schmitt trigger circuit at 3 Volt                                                                                                 |

|      | supply                                                                                                                                                                       |

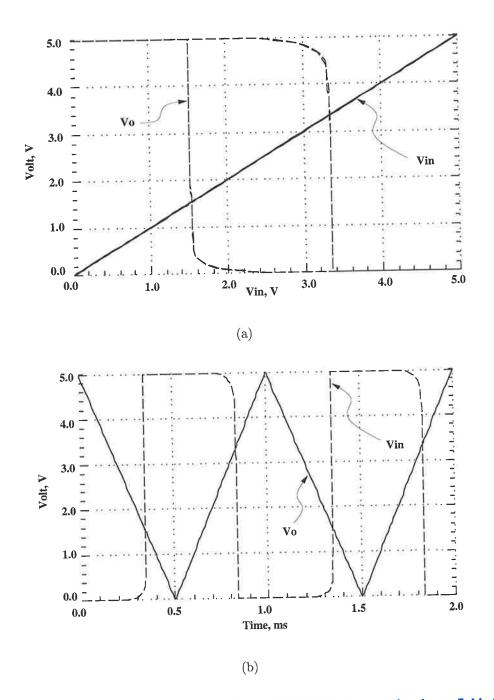

| 4.30 | Measured characteristics of the fabricated Schmitt trigger circuit at 5 Volt                                                                                                 |

|      | supply                                                                                                                                                                       |

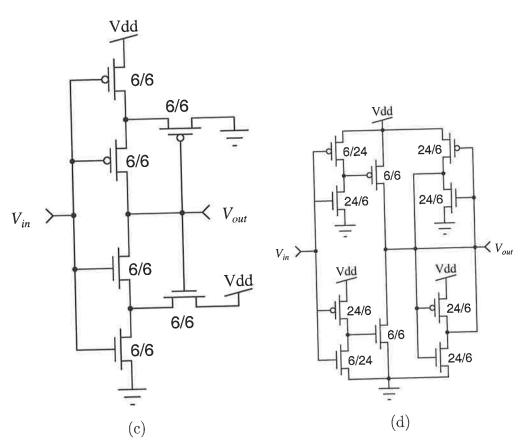

| 4.31 | A collection of commonly used CMOS Schmitt trigger circuits in literature, $127$                                                                                             |

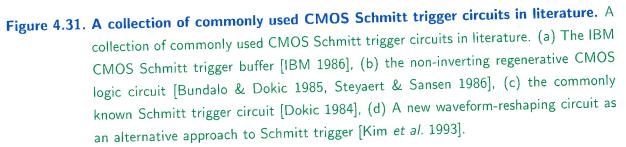

| 4.32 | Simulated input-output characteristics of the common Schmitt trigger cir-                                                                                                    |

|      | cuits                                                                                                                                                                        |

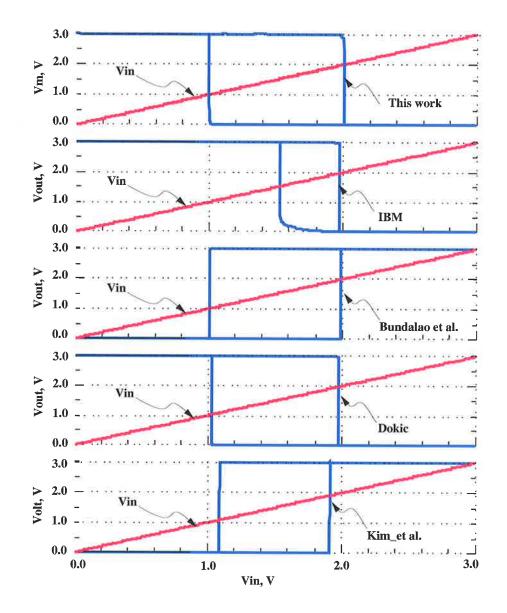

| 4.33 | Simulated current drawn from the supply voltage as function of the input                                                                                                     |

|      | signal for the commonly known Schmitt trigger circuits                                                                                                                       |

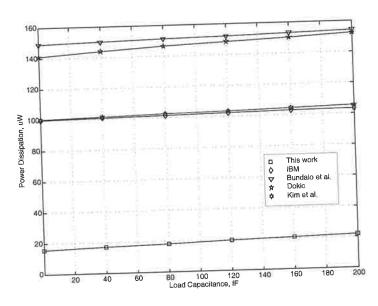

| 4.34 | Measured RMS power dissipation from simulations for the commonly known                                                                                                       |

|      | Schmitt trigger types as function of a load capacitance. $\dots \dots \dots$ |

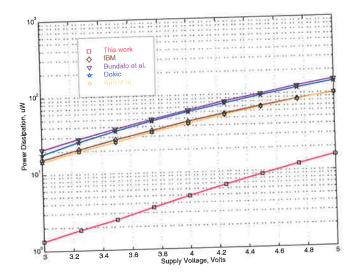

| 4.35 | Measured RMS power dissipation from simulations for the commonly known                                                                                                       |

|      | Schmitt trigger circuits as function of the supply voltage                                                                                                                   |

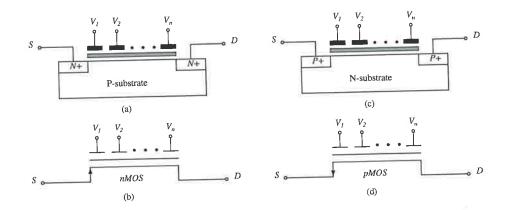

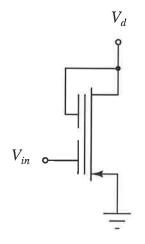

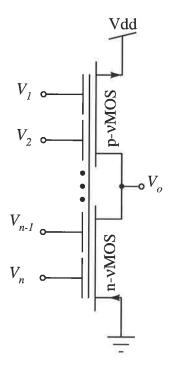

| 5.1  | The basic structure and symbol of $\nu$ MOS transistor                                                                                                                       |

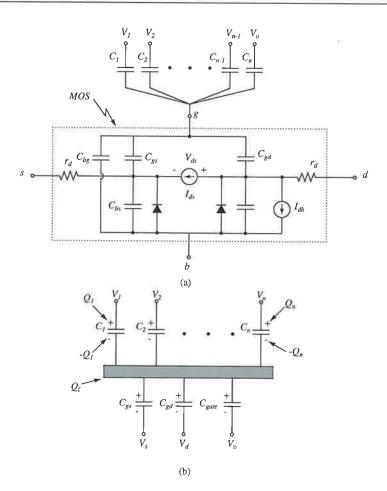

| 5.2  | Equivalent circuit and capacitance representation of $\nu MOS$ transistor 140                                                                                                |

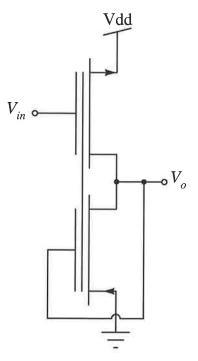

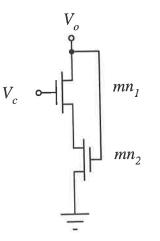

| 5.3  | Grounded active resistor design based on $\nu MOS$ transistor                                                                                                                |

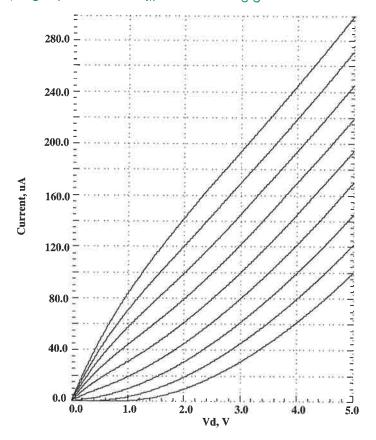

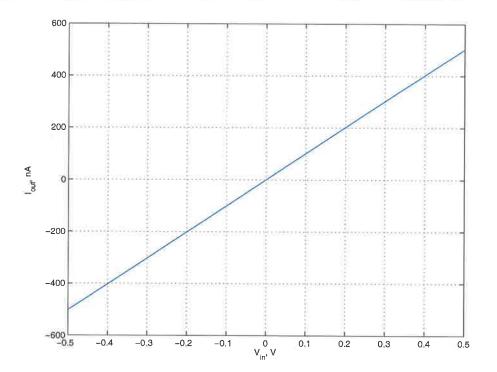

| 5.4  | Neuron-grounded resistor simulation                                                                                                                                          |

| 5.5  | A controlled gain amplifier circuit designed using linear grounded resistors. 146                                                                                            |

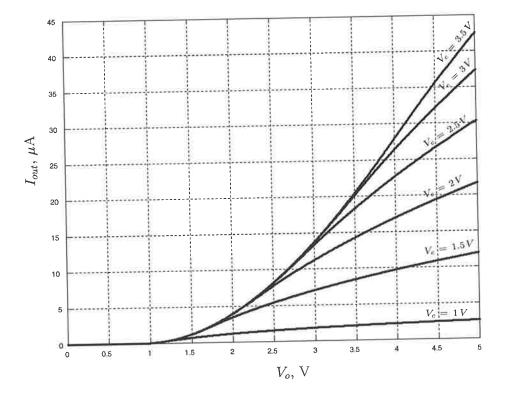

| 5.6  | The simulation results of the controlled gain amplifier circuit which uses                                                                                                   |

|      | $\nu MOS$ transistors                                                                                                                                                        |

| 5.7  | A schematic circuit diagram of a 'neuron-inverter.'                                                                                                                          |

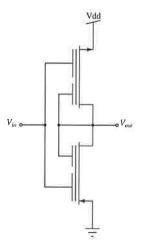

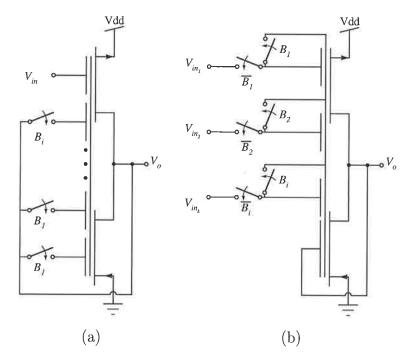

| 5.8  | A schematic diagram of a controlled gain amplifier using $\nu$ CMOS inverter. 148                                                                                            |

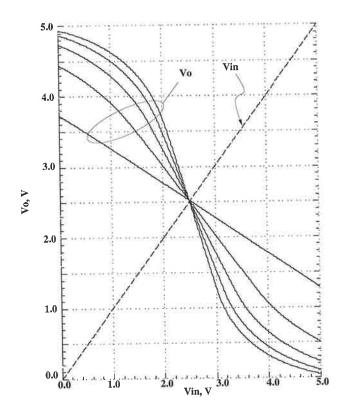

| 5.9  | The simulation results of the neuron controlled gain amplifier circuit. $\dots$ 149                                                                                          |

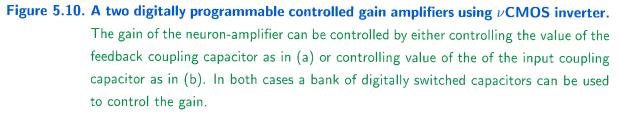

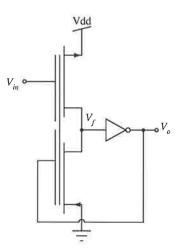

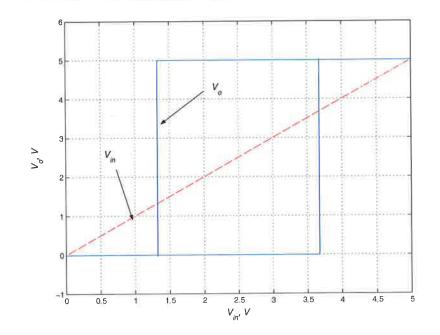

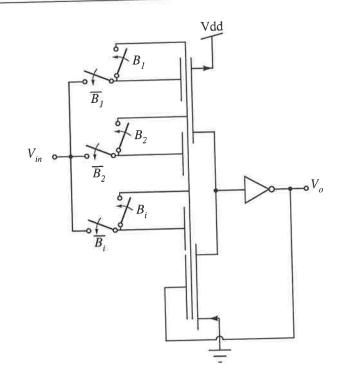

| 5.10 | A two digitally programmable controlled gain amplifiers using $\nu \text{CMOS}$ in-                                                                                          |

|      | verter                                                                                                                                                                       |

|      |                                                                                                                                                                              |

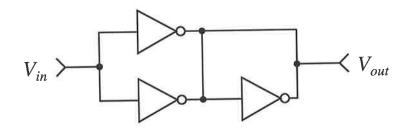

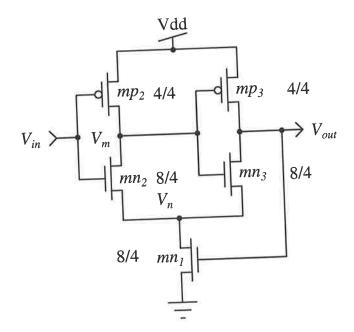

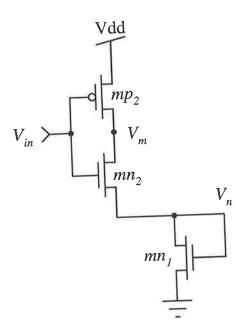

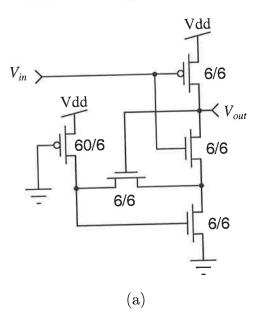

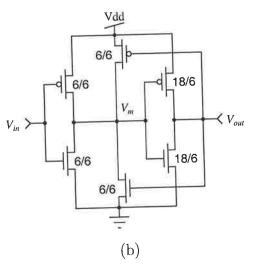

| 5.11 | Neuron-Schmitt trigger circuit                                                                                                                                   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

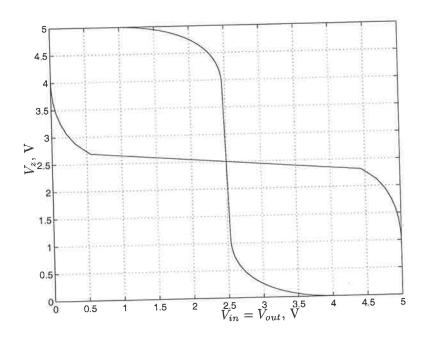

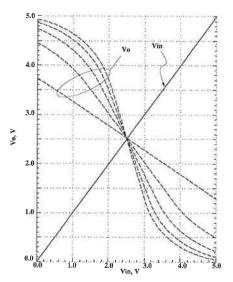

| 5.12 | The simulation results of the neuron-Schmitt trigger shown in Figure 5.11. 153                                                                                   |

| 5.13 | The simulation results of a Schmitt trigger shown in Figure 5.11 with                                                                                            |

|      | buffered output                                                                                                                                                  |

| 5.14 | A conceptual Digitally adjustable neuron-Schmitt trigger hysteresis 155                                                                                          |

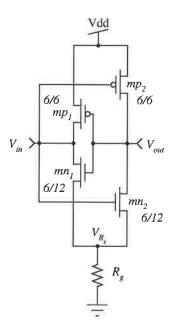

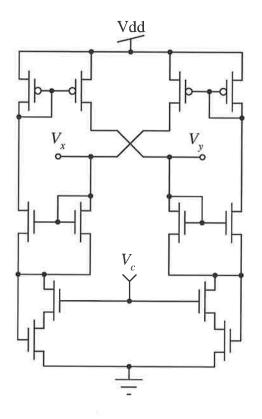

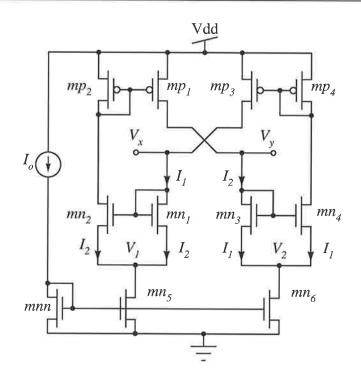

| 5.15 | A low power controlled gain neuron-amplifier                                                                                                                     |

| 5.16 | Simulation results of the low power controlled gain neuron-amplifier 157                                                                                         |

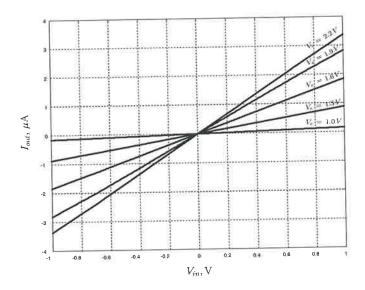

| 5.17 | The measured input-output characteristics from fabricated neuron-amplifier.158                                                                                   |

| 5.18 | The measured input-output characteristics of the neuron-Schmitt trigger                                                                                          |

|      | circuit                                                                                                                                                          |

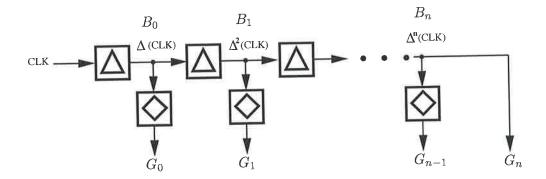

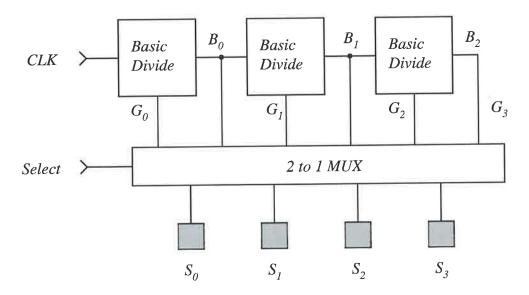

| 6.1  | A block diagram of an N-bit Gray code counter                                                                                                                    |

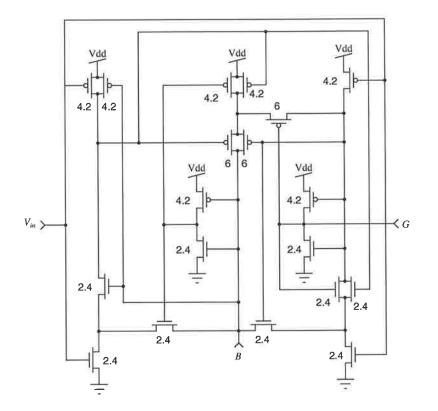

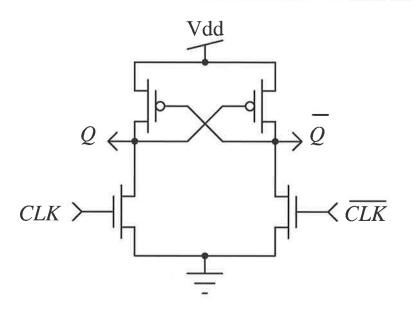

| 6.2  | Circuit diagram of the optimised divide by two circuit                                                                                                           |

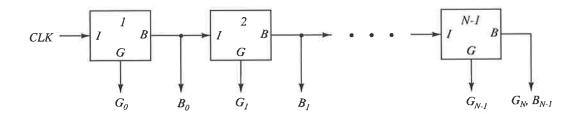

| 6.3  | Block diagram of an N bit Gray code counter. $\dots \dots \dots$ |

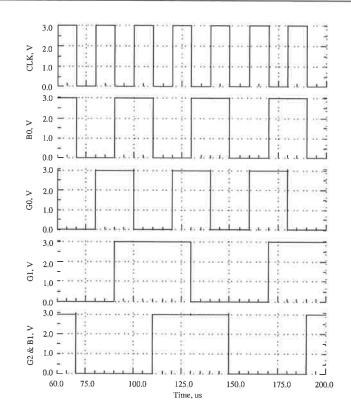

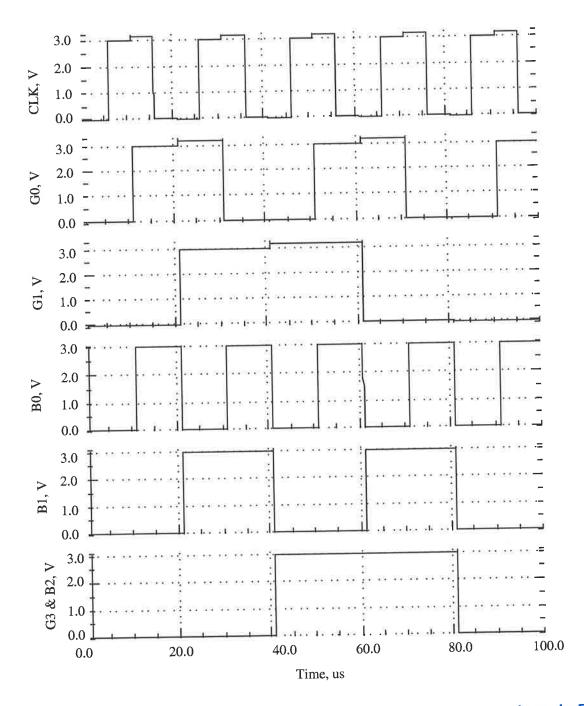

| 6.4  | The simulation results for a 3-bit Gray and 2-bit binary code counter $174$                                                                                      |

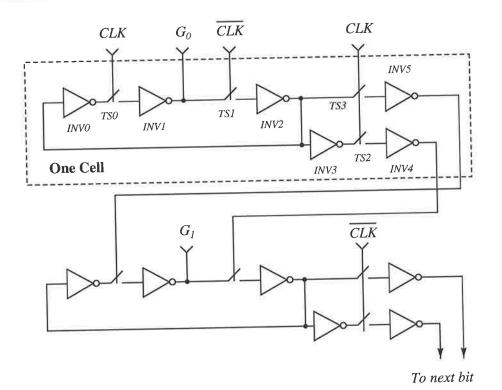

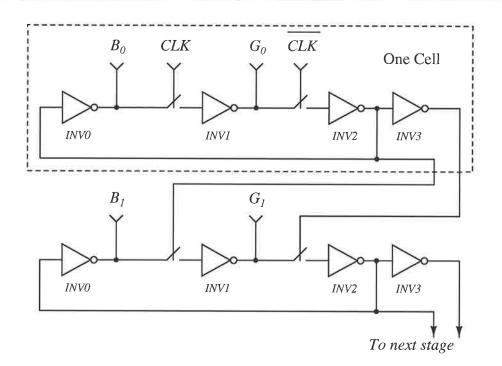

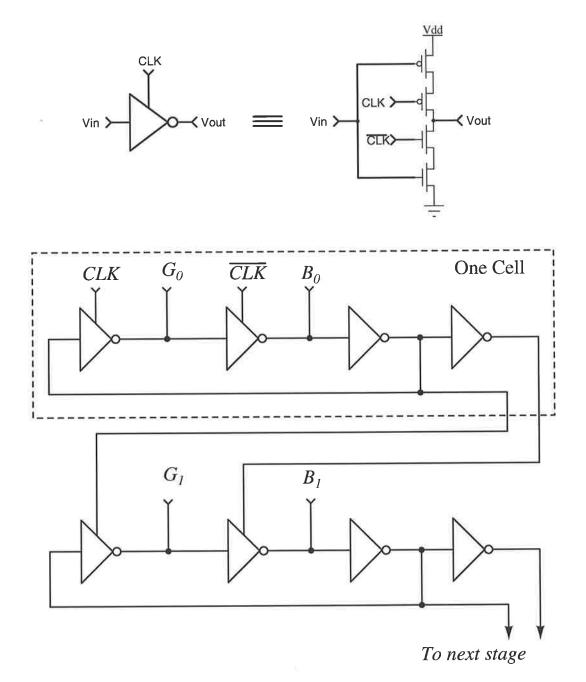

| 6.5  | A schematic diagram of the dynamic Gray code counter                                                                                                             |

| 6.6  | A schematic diagram of the new dynamic Gray-binary counter that uses                                                                                             |

|      | inverters and transmission gates                                                                                                                                 |

| 6.7  | A schematic diagram of the new dynamic Gray-binary counter using clocked                                                                                         |

|      | inverters                                                                                                                                                        |

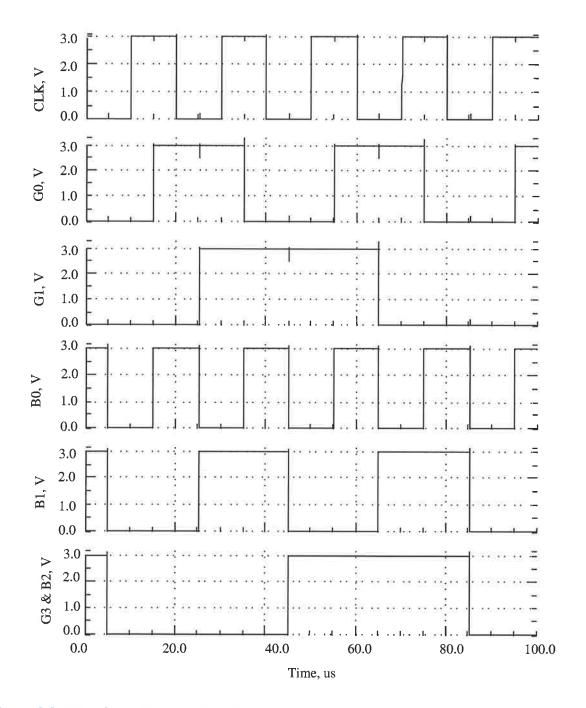

| 6.8  | The simulation results of the new dynamic Gray-binary counter shown in                                                                                           |

|      | Figure 6.6                                                                                                                                                       |

| 6.9  | The simulation results of the new dynamic Gray-binary counter shown in                                                                                           |

|      | Figure 6.7                                                                                                                                                       |

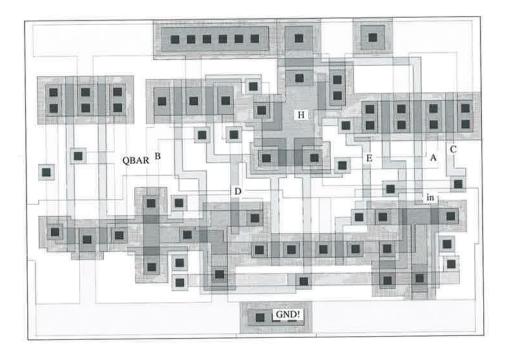

| 6.10 | An inverter circuit using CVSL family                                                                                                                            |

| 6.11 | Compact layouts of the optimised JK flip-flop shown in Figure 6.2 181                                                                                            |

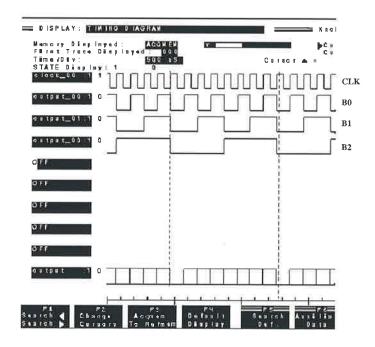

| 6.12 | A block diagram of the fabricated 4 bit Gray – 3 bit binary counter 181                                                                                          |

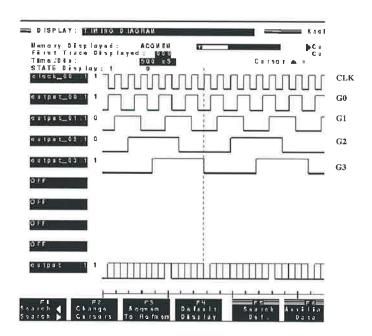

| 6.13 | Measured results from the fabricated 4 bit Gray – 3 bit Gray-binary counter. $182$                                                                               |

| 6.14 | Measured results from the fabricated 4 bit Gray – 3 bit binary counter 182                                                                                       |

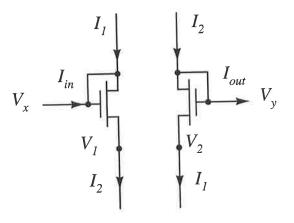

| 7.1  | The basic MOS transistor cell                                                                                                                                    |

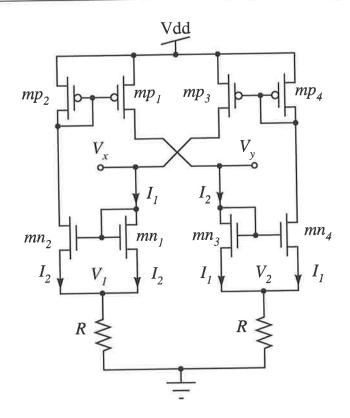

| 7.2  | The new topology with two passive resistor connected at $V_1$ and $V_2$ and                                                                                      |

|      | ground                                                                                                                                                           |

| 7.3  | The simulation results of the new circuit topology with two 1 M $\Omega$ passive                                                                                 |

|      | resistors connected at $V_1$ and at $V_2$ of Figure 7.2. $\ldots \ldots \ldots \ldots \ldots \ldots 192$                                                         |

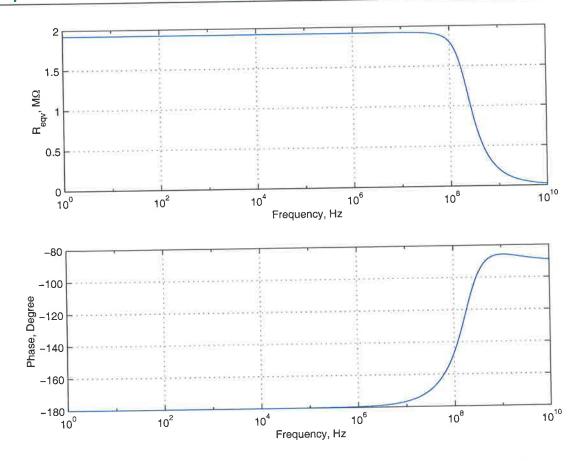

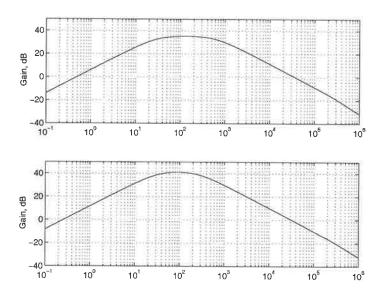

| 7.4  | The frequency response of the new circuit topology with two 1 M $\Omega$ passive                                                                                 |

|      | resistors connected at $V_1$ and $V_2$                                                                                                                           |

į,

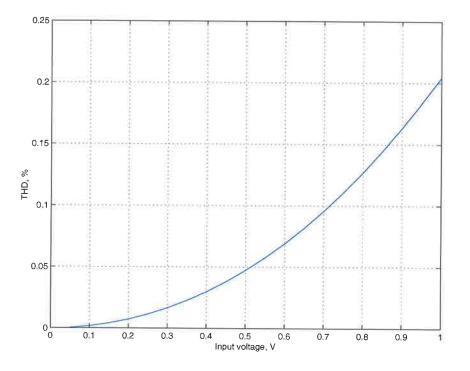

| 7.5  | The total harmonic distortion (THD) introduced by the new circuit topol-                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------|

|      | ogy as function of the input signal amplitude                                                                                       |

| 7.6  | A very linear grounded resistor                                                                                                     |

| 7.7  | Simulation results of the grounded resistor shown in Figure 7.6 195                                                                 |

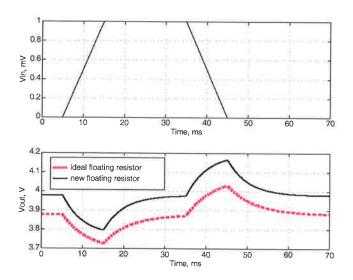

| 7.8  | A voltage controlled floating resistor                                                                                              |

| 7.9  | Simulation results of the new voltage controlled floating resistor shown in                                                         |

|      | Figure 7.8                                                                                                                          |

| 7.10 | A very high value current controlled floating resistor                                                                              |

| 7.11 | Simulation results of the current controlled very high value floating resistor                                                      |

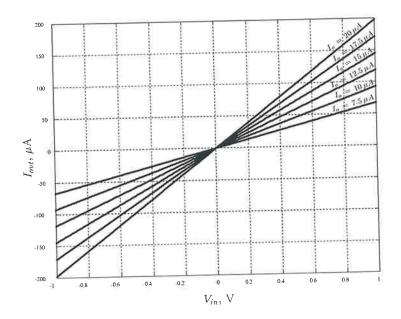

|      | with large reference current values                                                                                                 |

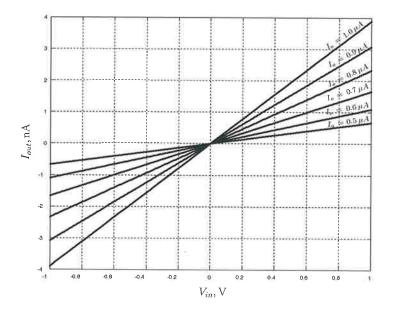

| 7.12 | The simulation results of the very high value floating resistor with small                                                          |

|      | reference current values. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $200$                             |

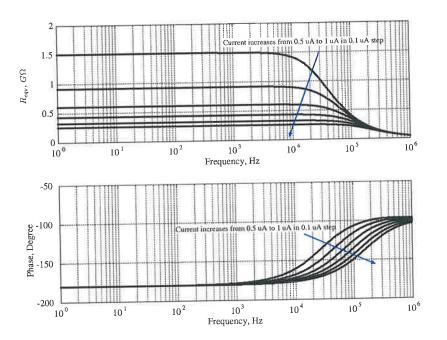

| 7.13 | The frequency response of the very high value floating resistor with the                                                            |

|      | small value of reference current                                                                                                    |

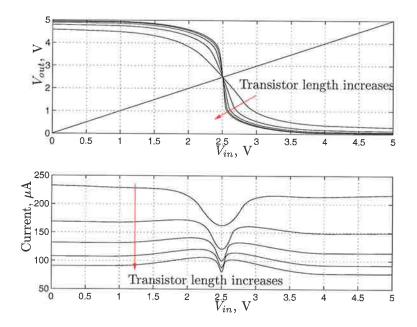

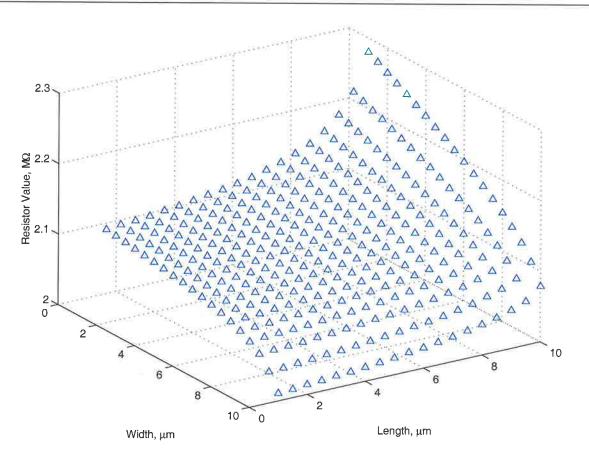

| 7.14 | The effect of transistor width and length on the circuit topology effective                                                         |

|      | floating resistance                                                                                                                 |

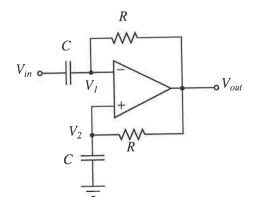

| 7.15 | A circuit diagram of a low frequency differentiator circuit                                                                         |

| 7.16 | The frequency response of the bandpass filter circuit                                                                               |

| 7.17 | The simulation results of the bandpass filter circuit for an input pulse. $\therefore$ 204                                          |

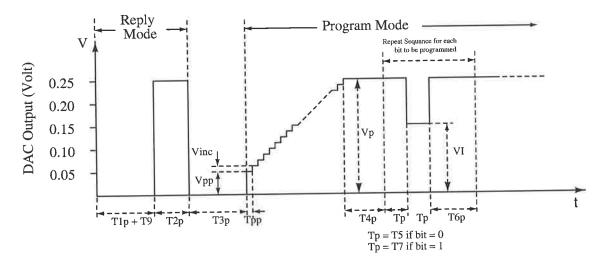

| 8.1  | A simplified block diagram of the ISD9664 chip                                                                                      |

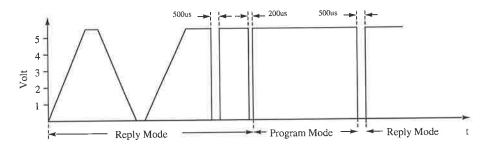

| 8.2  | Test waveform for the PMD circuit                                                                                                   |

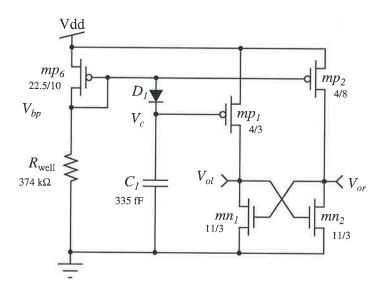

| 8.3  | The circuit diagram of Version-1 of PMD circuit.                                                                                    |

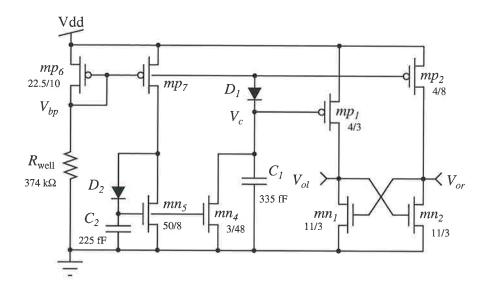

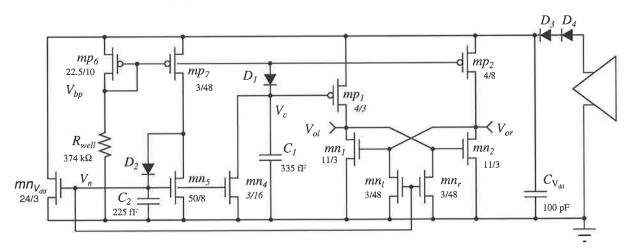

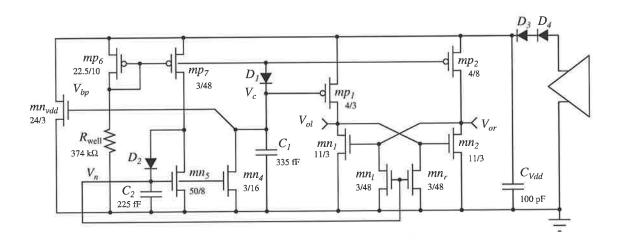

| 8.4  | The circuit diagram of Version-2 of PMD circuit.                                                                                    |

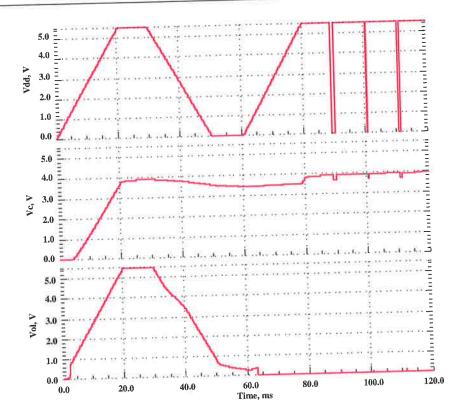

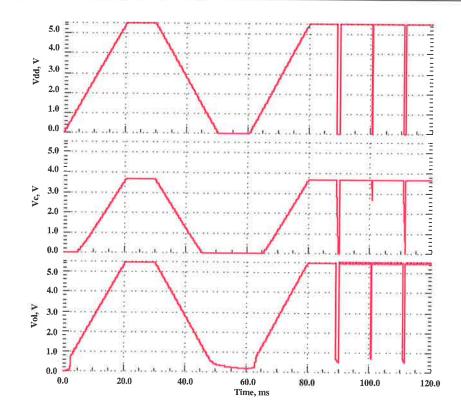

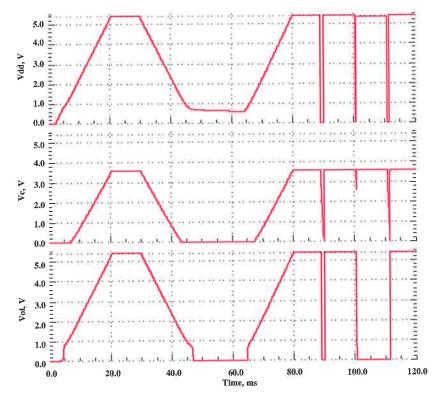

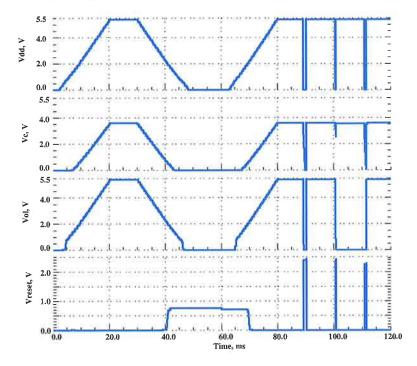

| 8.5  | Simulation results for Version-1 PMD circuit.                                                                                       |

| 8.6  | Simulation results for Version-2 PMD circuit with the new transistors ad-                                                           |

|      | justments                                                                                                                           |

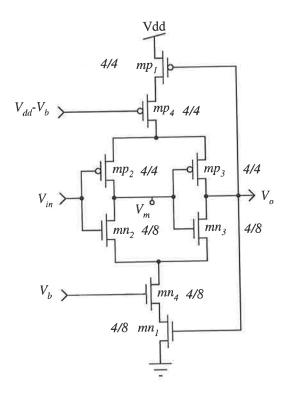

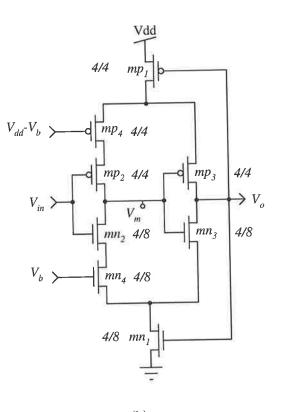

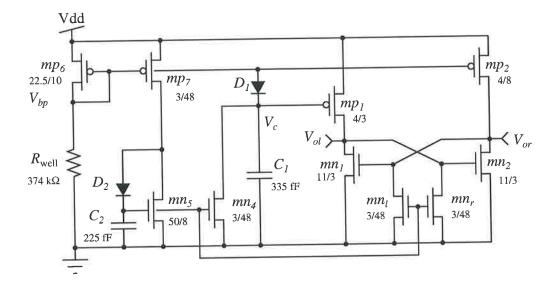

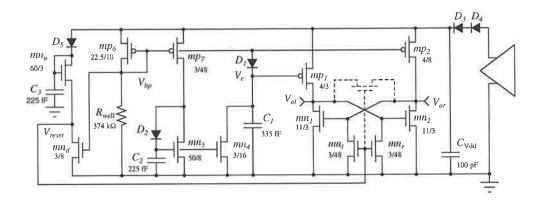

| 8.7  | The circuit diagram of Version-3 of PMD circuit.                                                                                    |

| 8.8  | The simulation results of Version-3 PMD circuit                                                                                     |

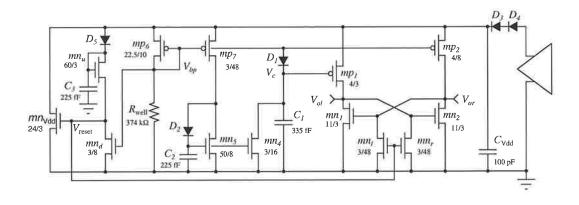

| 8.9  | The circuit diagram of Version-4 of PMD circuit.                                                                                    |

| 8.10 | The circuit diagram of a PMD circuit that uses node $V_n$ to statically bleed-                                                      |

|      | ing the supply capacitance. $\ldots \ldots 221$ |

| 8.11 | The circuit diagram of the PMD circuit that uses node $V_c$ to statically                                                           |

|      | bleed the supply capacitance                                                                                                        |

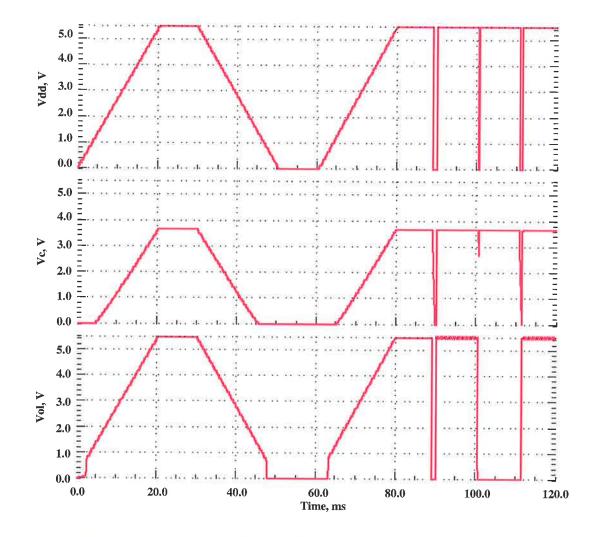

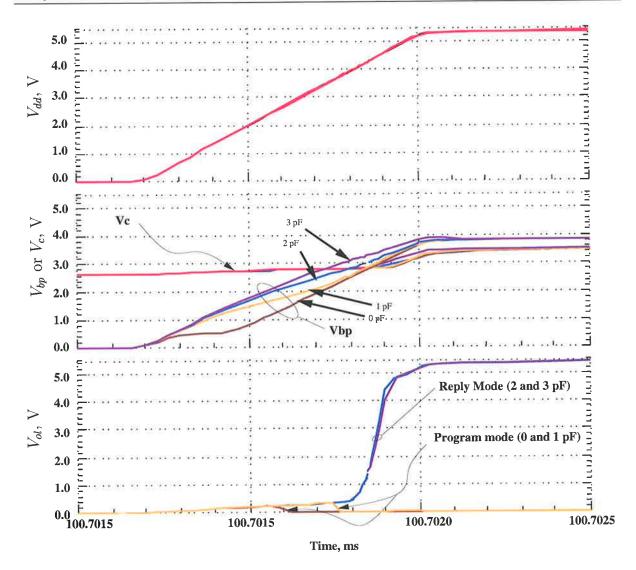

| 8.12 | The simulation results of the PMD circuit shown in Figure 8.10                                                                      |

| 8.13 | The circuit diagram of the PMD circuit that uses a dynamic bleed. $\ldots$ 224                                                      |

|      |                                                                                                                                     |

| The simulation results of the PMD circuit shown in Figure 8.13                       |

|--------------------------------------------------------------------------------------|

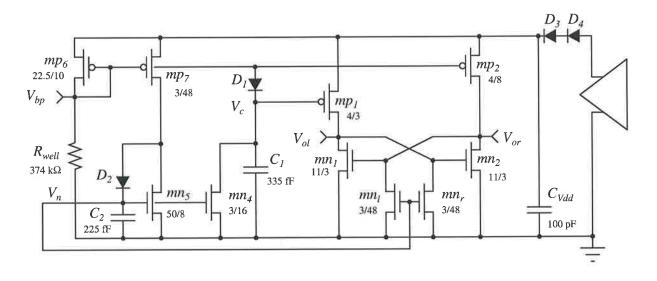

| The circuit diagram of the PMD circuit that uses a dynamic approach to               |

| reset the voltage at $V_{ol}$ and $V_{or}$                                           |

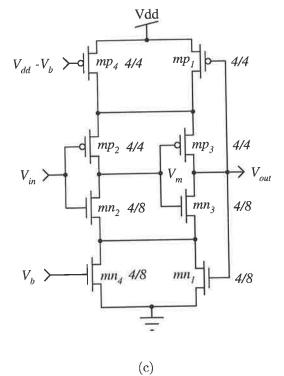

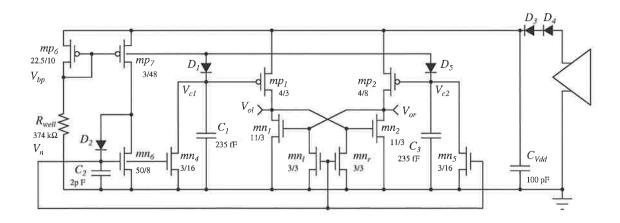

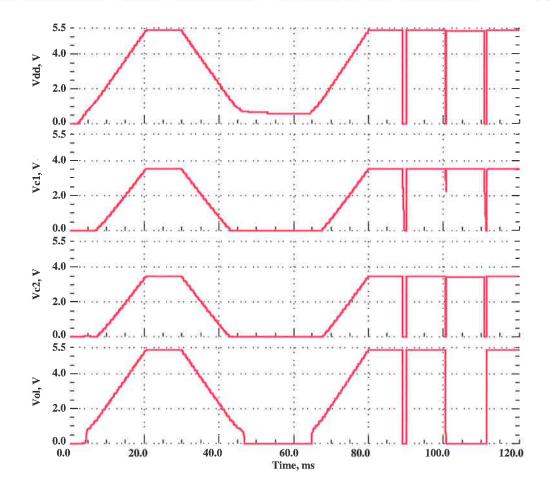

| A fully symmetrical PMD circuit with fully isolated terminals from supply            |

| coupling                                                                             |

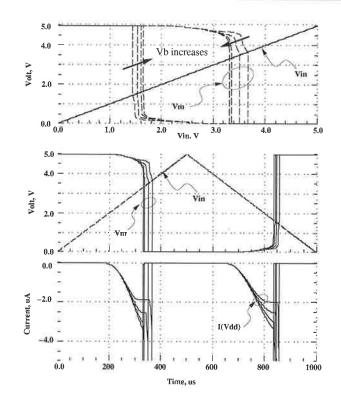

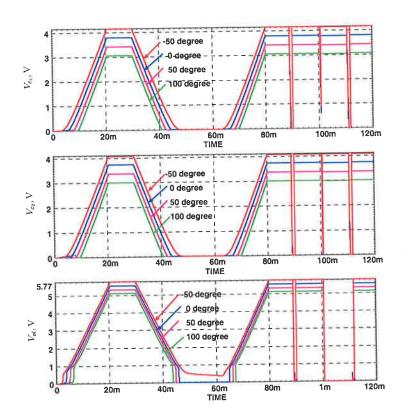

| Simulation results of a fully symmetrical PMD circuit with the circuit tem-          |

| perature was swept from -50 °C to 100 °C in 50 °C steps                              |

| The output of the analog to digital converter that was used to control the           |

| RF attenuator for measuring the PMD circuit within RF environment 227                |

| The simulation results of the PMD circuit with different values of coupling          |

| capacitors between the supply voltage and $V_{bp}$                                   |

| The simulation results of a fully symmetrical PMD circuit with different             |

| coupling capacitors from the supply voltage to $V_{bp}$                              |

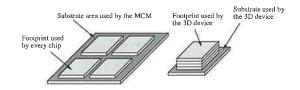

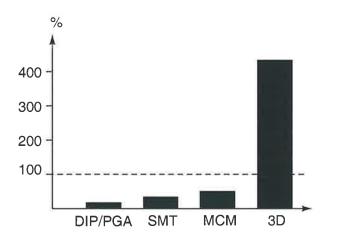

| 3D packaging technology silicon efficiency                                           |

| Silicon efficiency comparison between 3D packaging technology and other              |

| conventional packaging                                                               |

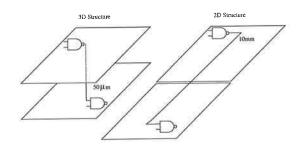

| A comparison between the wiring lengths in 2D and 3D structures. $\ldots$ 249        |

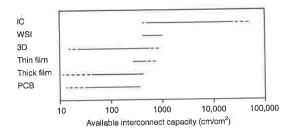

| Available interconnect capacity for different technologies (cm/cm <sup>2</sup> ) 251 |

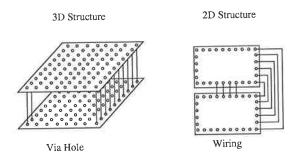

| A comparison between 3D and 2D structures in terms of the possible num-              |

| ber of interconnections assuming one routing layer for the 2D structure 251 $$       |

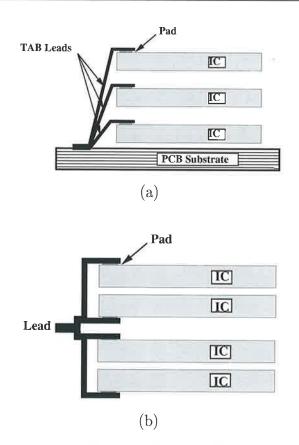

| Stacked tape carrier vertical interconnect                                           |

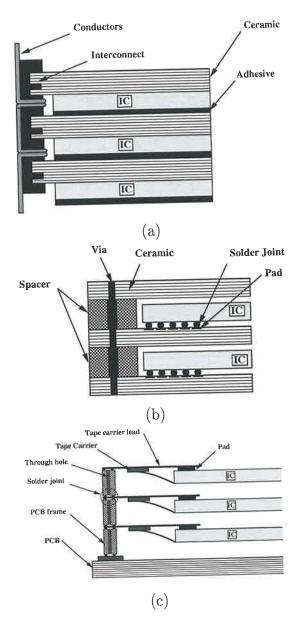

| Solder edge conductors vertical interconnections                                     |

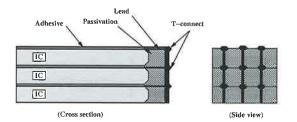

| A thin film metal "T-connects" for vertical interconnections                         |

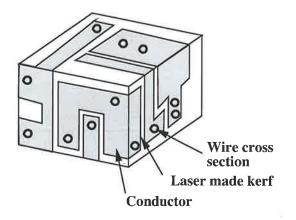

| Direct laser writing process                                                         |

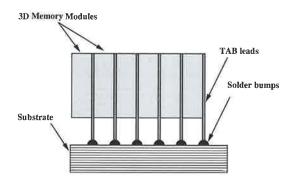

| TAB leads soldered to bumps                                                          |

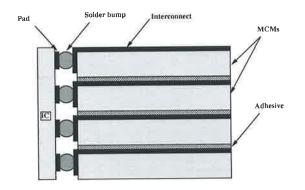

| Flip bonded chip to stacked MCMs                                                     |

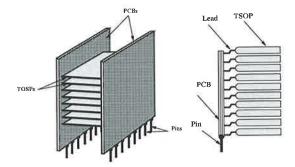

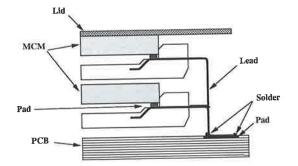

| PCB solder to TSOPs                                                                  |

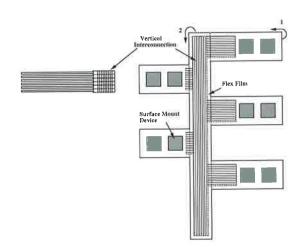

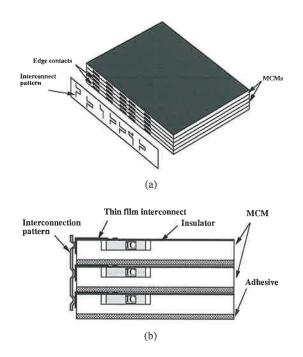

| Flex type vertical interconnects                                                     |

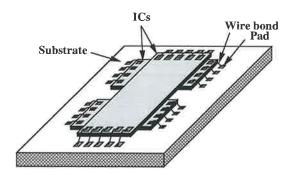

| Wire bonding interconnection                                                         |

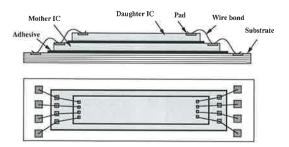

| Stacked chips interconnected using wire bonding                                      |

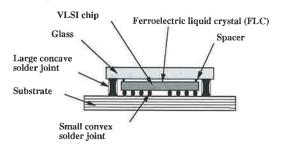

| Stacked chips using flip-chip technology                                             |

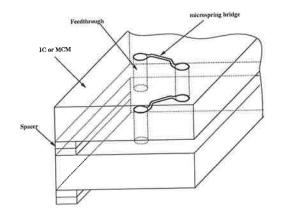

| Microspring interconnection                                                          |

| Solder leads on stacked MCMs                                                         |

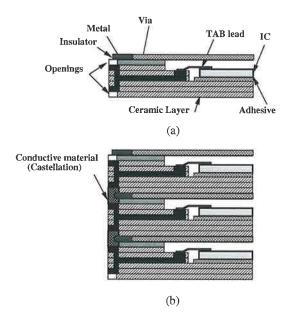

| Edge interconnection on the sides of the cube                                        |

| Blind castellation vertical interconnection                                          |

|                                                                                      |

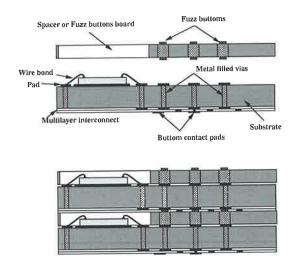

| A.21 | Array contacts between MCMs                                                |

|------|----------------------------------------------------------------------------|

| A.22 | A schematic diagram of TUB stacking technology.                            |

| A.23 | Vertical interconnections using anisotropic conductive material.           |

| A.24 | Solder balls for area interconnect stacking                                |

| A.25 | Wafer scale stacking                                                       |

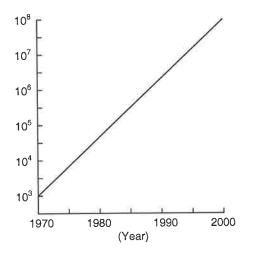

| A.26 | Moore's Law for active element density                                     |

| D.1  | Conventional integrator oscillator                                         |

| D.2  | Extended mode integrator oscillator (EMSO)                                 |

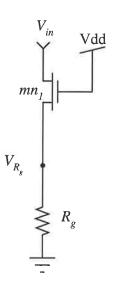

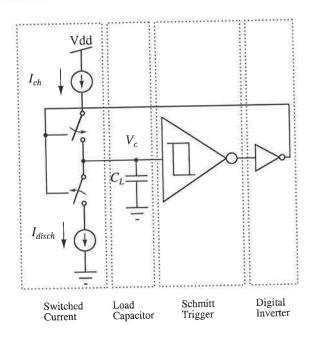

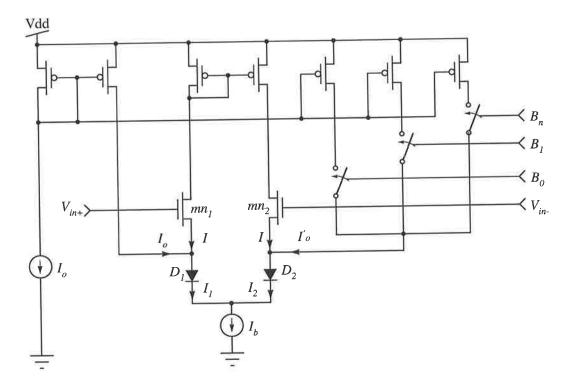

| D.3  | Circuit diagram of a conventional Schmitt-Oscillator                       |

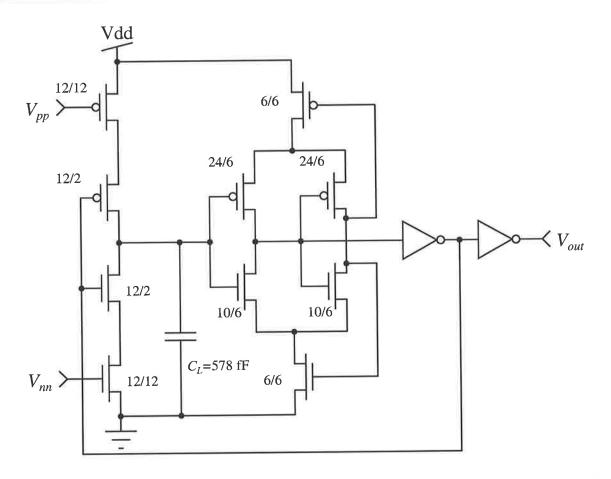

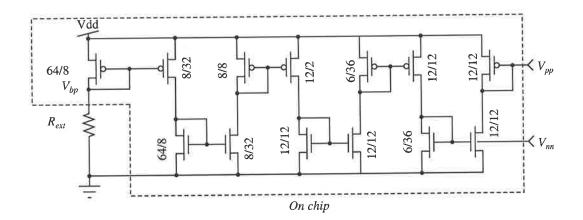

| D.4  | Circuit diagram of the bias circuit used in biasing the different types of |

|      | oscillators                                                                |

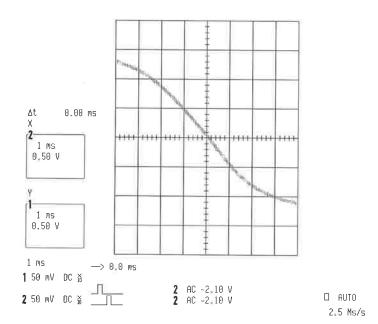

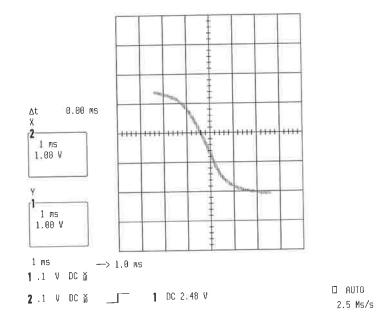

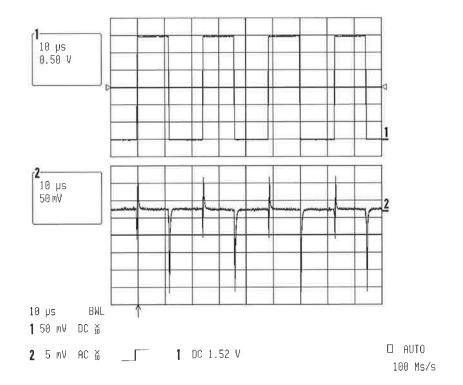

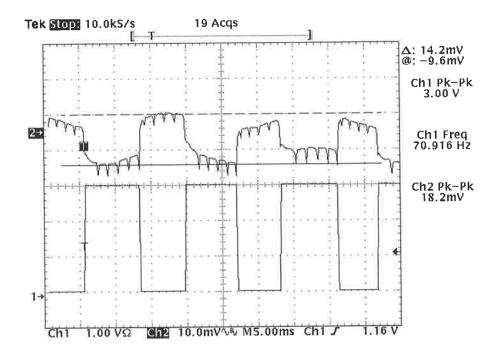

| D.5  | An oscilloscope photograph of the measured output of the conventional      |

|      | Schmitt-Oscillator (Screen dump from the LeCroy 9360 Oscilloscope) 302     |

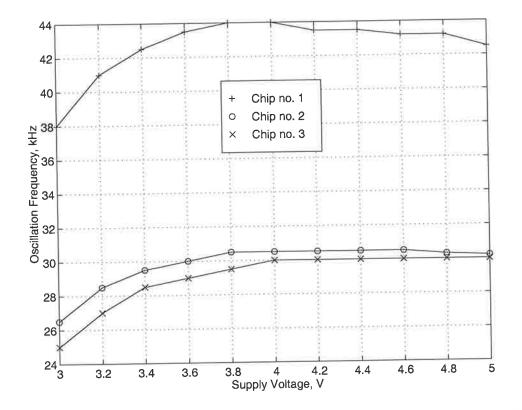

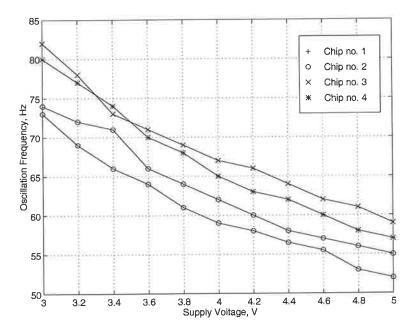

| D.6  | The measured frequency variation of the conventional Schmitt-Oscillator    |

|      | as function of the supply voltage                                          |

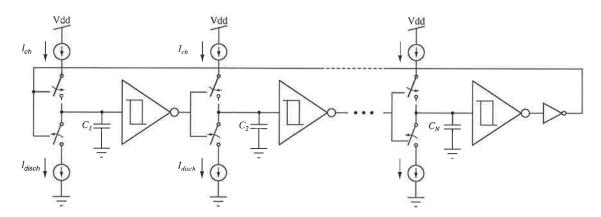

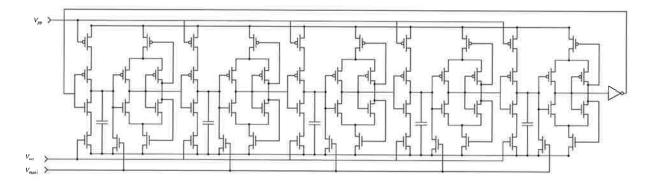

| D.7  | The circuit connectivity diagram of an EMSO that uses 5 integrators $304$  |

| D.8  | The measured oscillation frequency of the EMSO which uses five integrators |

|      | at 3 Volt supply voltage                                                   |

| D.9  | The measured oscillation frequency of the EMSO as function of the supply   |

|      | voltage                                                                    |

| E.1  | Digitally trimmed differential amplifier analysis                          |

# List of Tables

| 1.1 | The research contributions for low power mixed signal design techniques.           | 5   |

|-----|------------------------------------------------------------------------------------|-----|

| 1.2 | A list of nominal voltages for various chemical battery technologies.              | 8   |

| 2.1 | The STC amplifier gain as function of the Taiwan Semiconductor Manu-               |     |

|     | facturing Company (TSMC) process skew parameters.                                  | 34  |

| 2.2 | The PTC amplifier gain as function of the TSMC process skew parameters.            | 38  |

| 2.3 | The gain of the digitally controlled amplifier as function of the digital input    |     |

|     | combinations                                                                       | 43  |

| 2.4 | A comparison between the three amplifier circuits                                  | 57  |

| 3.1 |                                                                                    | 65  |

| 3.2 | Rules for Optimum Matching                                                         | 66  |

| 3.3 | Introduced offset voltage as function of the current mismatch.                     | 79  |

| 3.4 | The transistor sizes of the digitally programmable arms.                           | 84  |

| 3.5 | Minimum voltage difference measured between the trimmer's arms from                |     |

|     | four fabricated chips.                                                             | 85  |

| 4.1 | Statistical results of the low power Schmitt trigger circuit shown in Figure 4.8.1 | 06  |

| 4.2 | Comparison between measured and simulated characteristics of the fabri-            |     |

|     | cated low power Schmitt trigger circuits                                           | 17  |

| 6.1 | A four bit Gray code sequence referenced to input clock states                     | 70  |

| 8.1 | Parameter values                                                                   | 28  |

| A.1 | 3D Mass memory volume and weight comparisons                                       | 247 |

| A.2 | Institutions active in 3D packaging                                                | 270 |

| A.3 | Institutions active in 3D packaging                                                | 271 |

| A.4 | Evaluation of companies according to their method of periphery intercon-           |     |

|     | nection between stacked ICs                                                        | 273 |

|     |                                                                                    |     |

| A.5 | An evaluation of companies which provides area interconnection between       |

|-----|------------------------------------------------------------------------------|