# Mapping of Processing Elements of Hardware-based Production Systems on Networks on Chip

by

#### Mostafa Wasiuddin Numan

B. Sc. (Engineering) in Computer Science and Engineering Shahjalal University of Science and Technology, Bangladesh, 2006

M. Sc. (By Research) in Electrical, Electronic and Systems Engineering National University of Malaysia (UKM), Malaysia, 2010

Thesis submitted for the degree of

**Doctor of Philosophy**

in

Electrical and Electronic Engineering Faculty of Engineering, Computer and Mathematical Sciences The University of Adelaide, Australia

#### **Supervisors:**

Professor Michael Liebelt Dr Braden J. Phillips To my dearest parents, to my wonderful wife, Fathima, and our little princess, Zoharin, to my sister, Mili, and brother, Shahan, without whom none of my success would be possible.

## **Contents**

| Conten  | ııs      |                                             | V    |

|---------|----------|---------------------------------------------|------|

| Declara | ation    |                                             | ix   |

| Acknow  | wledgm   | ients                                       | xi   |

| Conve   | ntions   |                                             | xiii |

| Abstra  | ct       |                                             | xv   |

| List of | Figures  |                                             | xvii |

| List of | Tables   |                                             | xxi  |

| Chapte  | er 1. In | troduction                                  | 1    |

| 1.1     | Backg    | round                                       | 2    |

| 1.2     | Resear   | rch motivations                             | 4    |

| 1.3     | Thesis   | s objectives                                | 5    |

| 1.4     | Staten   | nent of original contributions              | 6    |

|         | 1.4.1    | On-chip communication of cognitive workload | 6    |

|         | 1.4.2    | Optimised mapping techniques                | 7    |

| 1.5     | Overv    | iew of the thesis                           | 7    |

| Chapte  | er 2. Ba | ckground and Related Work                   | 11   |

| 2.1     | Introd   | uction                                      | 12   |

| 2.2     | Artific  | rial general intelligence                   | 13   |

| 2.3     | Cogni    | tive architectures                          | 14   |

|         | 2.3.1    | Characteristics of cognitive architectures  | 16   |

|         | 2.3.2    | Related work on cognitive architectures     | 17   |

|         | 2.3.3    | Soar                                        | 19   |

|         |          |                                             |      |

|        | 2.3.4   | ACT-R                                            | 22 |

|--------|---------|--------------------------------------------------|----|

| 2.4    | Produ   | action systems                                   | 24 |

|        | 2.4.1   | Basic structure of production systems            | 24 |

|        | 2.4.2   | Related work on production systems               | 26 |

| 2.5    | Multi-  | -processor systems on chip                       | 28 |

| 2.6    | Netwo   | orks on chip                                     | 30 |

|        | 2.6.1   | NoC communication model                          | 31 |

|        | 2.6.2   | Related work on NoC architectures                | 33 |

|        | 2.6.3   | Related work on NoCs mapping                     | 34 |

| 2.7    | Chapt   | er summary                                       | 35 |

| Chapte | r 3. Ha | ardware-based Production System                  | 37 |

| 3.1    | Introd  | luction                                          | 38 |

| 3.2    | Produ   | action systems                                   | 39 |

|        | 3.2.1   | Rete matching algorithm                          | 40 |

|        | 3.2.2   | TREAT                                            | 41 |

| 3.3    | Street  | Processor: Hardware-based production system      | 42 |

| 3.4    | Street  | language                                         | 43 |

|        | 3.4.1   | Working memory                                   | 44 |

|        | 3.4.2   | Production rules                                 | 44 |

|        | 3.4.3   | Synchronisation                                  | 48 |

| 3.5    | Street  | Processor architecture                           | 50 |

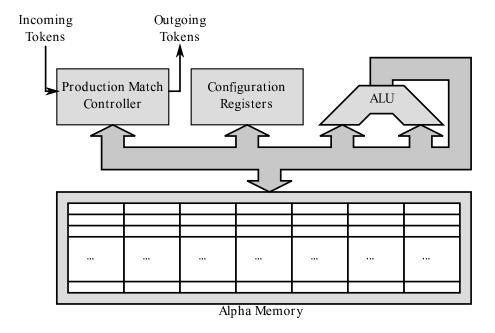

|        | 3.5.1   | Micro-architecture of a productor                | 50 |

|        | 3.5.2   | Big Productor                                    | 52 |

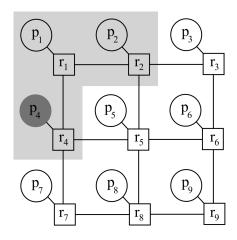

| 3.6    | Deper   | ndency graph                                     | 53 |

| 3.7    | Sleep   | period                                           | 54 |

| 3.8    |         | usion                                            | 55 |

| Chapte | r 4. In | terconnect Platform of SoCs with Homogeneous PEs | 57 |

| 4.1    |         | luction                                          | 58 |

| 4.2    |         | ations of conventional on-chip communication     | 58 |

|        |         | <u> -</u>                                        |    |

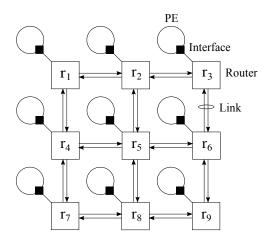

| 4.3         | NoC a      | architecture                                      | 59                   |

|-------------|------------|---------------------------------------------------|----------------------|

|             | 4.3.1      | Physical components                               | 60                   |

|             | 4.3.2      | Topology                                          | 61                   |

|             | 4.3.3      | Routing schemes                                   | 62                   |

|             | 4.3.4      | Routing implementation                            | 64                   |

|             | 4.3.5      | Flow control techniques                           | 65                   |

|             | 4.3.6      | Virtual channels                                  | 67                   |

| 4.4         | Route      | r micro-architecture                              | 67                   |

| 4.5         | NoC o      | of the Street Processor                           | 71                   |

| 4.6         | Concl      | usion                                             | 71                   |

| Charte      | F. M       | Toroning of Homogoneous PEs to No.C. Positors     | 70                   |

| 5.1         |            | apping of Homogeneous PEs to NoC Routers  luction | 73<br>74             |

| 5.1         |            |                                                   | 7 <del>4</del><br>75 |

| 5.3         |            | ing considerations                                | 75<br>76             |

| 3.3         | 5.3.1      | ing constraint and goal                           | 76                   |

|             | 5.3.2      | Problem definition                                | 78<br>78             |

| 5.4         |            | ated Annealing                                    | 79<br>79             |

| J. <b>4</b> | 5.4.1      | Simulated Annealing algorithm                     | 80                   |

|             | 5.4.2      | Annealing schedule                                | 80                   |

|             | 5.4.3      | Acceptance test                                   |                      |

|             | 5.4.4      | -                                                 | 82                   |

|             | 5.4.5      | Swapping function                                 | 82                   |

| 5.5         |            | h and Bound                                       | 82                   |

| 3.3         | 5.5.1      | Branch and Bound algorithm                        | 83                   |

|             | 5.5.2      | Lower bound cost calculation                      | 86                   |

|             | 5.5.3      | Upper bound cost calculation                      | 86                   |

| 5.6         |            | ase: the self-configurable Street agent           | 87                   |

| 5.0         | 5.6.1      | Entity relationship                               | 88                   |

|             | 5.6.2      | Production rules                                  | 89                   |

| 5.7         |            | iments                                            | 90                   |

| 5.8         | -          | rsis of Branch and Bound mapping                  | 90                   |

| 5.9         | -          | usion                                             | 96                   |

| الا.ق       | Conclusion |                                                   |                      |

| Chapte  | er 6. Pr | iority-based Simulated Annealing of Grouped PEs     | 97  |

|---------|----------|-----------------------------------------------------|-----|

| 6.1     | Introd   | luction                                             | 98  |

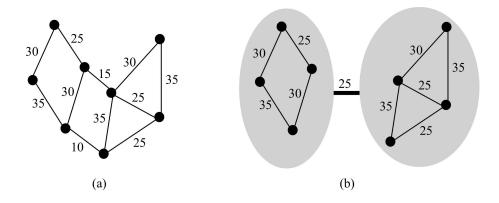

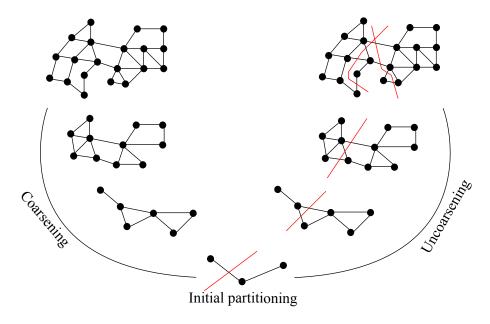

| 6.2     | Graph    | n partitioning                                      | 99  |

|         | 6.2.1    | Multi-level graph partitioning                      | 100 |

|         | 6.2.2    | Multi-level partitioning of traffic graph           | 103 |

| 6.3     | Priori   | ty-based Simulated Annealing                        | 104 |

|         | 6.3.1    | Initial mapping                                     | 104 |

|         | 6.3.2    | Annealing                                           | 107 |

| 6.4     | Test ca  | ase: the Subsumption Cockroach agent                | 108 |

|         | 6.4.1    | Subsumption architecture                            | 109 |

|         | 6.4.2    | Development of the Cockroach agent                  | 110 |

| 6.5     | Exper    | iments                                              | 111 |

| 6.6     | Concl    | usion                                               | 115 |

| Chapte  | er 7. Co | onclusions and Future Work                          | 119 |

| 7.1     | Summ     | nary                                                | 120 |

| 7.2     | Concl    | usions                                              | 122 |

| 7.3     | Future   | e work                                              | 123 |

| Appen   | dix A.   | List of Street Rules of the Self-configurable Agent | 127 |

| Appen   | dix B.   | List of Street Rules of the Cockroach Agent         | 131 |

| Bibliog | graphy   |                                                     | 141 |

| List of | Acrony   | rms                                                 | 155 |

| Publica | ations   |                                                     | 157 |

| Biogra  | phy      |                                                     | 159 |

## **Declaration**

I certify that this work contains no material, which has been accepted for the award of any other degree or diploma in my name, in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text.

I give consent to this copy of my thesis, when deposited in the University Library, being available for loan, photocopying, and dissemination through the library digital thesis collection subject to the provisions of the Copyright Act 1968.

I also give permission for the digital version of my thesis to be made available on the web, via the University's digital research repository, the Library Search, the Australian Digital Thesis Program (ADTP), and also through web search engines, unless permission has been granted by the University to restrict access for a period of time.

|        | September 26, 2017 |

|--------|--------------------|

| Signed | Date               |

## Acknowledgments

First and foremost, I take this opportunity to convey sincere gratitude to my supervisors, **Professor Michael Liebelt** and **Dr Braden J. Phillips** for their guidance and support throughout my candidature. Their remarkable expertise and unwavering optimism have always been helpful in propelling my research forward. I owe many thanks to my principal supervisor, Professor Liebelt for his generous knowledge sharing, insightful discussions and inspiring words in times of needs. His critical and thoughtful comments were always constructive and fruitful to improve the quality of my research. I am thankful to Dr Phillips for being a constant source of research ideas and constructive suggestions. I would like to gratefully acknowledge his enthusiastic supervision and encouraging attitude.

I recognise that this research would not have been possible without the financial support of Australian Government via a generous International Postgraduate Research Scholarship (IPRS) and Australian Postgraduate Award (APA).

There are many people who helped me throughout my PhD candidature. I would express appreciation to my colleagues and friends in the Centre for High Performance Integrated Technologies and Systems (CHiPTec), Jesse Frost, Francis Li, Peng Wang, Thanh Thi Thanh Bui, Simon Keen and Muhammad Usman Khan for their valuable comments time to time. My sincere gratitude goes to Jesse for his passion in discussing around different research issues and critical suggestions.

I am thankful to the office and support staff of the school for their kindness and assistance. I would also like to thank the head of the school, Associate Prof. Cheng-Chew Lim, for his support during my PhD research. In addition, I sincerely thank my friends and colleagues in the school, Syed Imranul Islam, Mehdi Kasaei, Dr Amir Ebrahimi, Dr Sarah Immanuel, Robert Moric, Madhulika Tripathi, Yansong (Garrison) Gao, Nicholas P. Lawrence, Dr Sam Darvishi, Shengjian (Jammy) Chen, Dr Ali Karami, Dr Zahra Shaterian, Mariam Ebrahimpour, Dr Mostafa Rahimi and Nazmul Huda for making such a friendly research environment. It has been a privilege to get acquainted with so many talented individuals.

I appreciate the selfless support of my friends, Dr Md. Ayub, Kingshuk Nandy, Dr Manabendra Saha, Dr Raihan Rumman, Shuvra Shaha, Asafuddoulah Suzon, Javed Hussain, Hassan Jahangir and Dr Zaheed Hasssan for making life so easy since my very early days in Adelaide. I also thank my good old friends, Majba Uddin, Saiful Islam, Rumon Rahman, Zaidul Alam, Razeeb Saleheen, Amit Roy and their families for always staying around me and my family. You all make me feel at home while away from home.

My endless gratitude goes to my parents, who always bestowed me with infinite support, wishes and continuous love. They always wanted me to be a 'doctor' (physician). I somehow failed to pursue their dreams, but they never complained, rather encouraged me for whatever I did. I hope, they can now get a contentment seeing 'Dr' in front of my name. Abbu and Ammu, you are the best blessings of Almighty Allah to me. I also thank Apamoni, Dulabhai and Najnin for their tremendous support and inspiration throughout my journey. As always, my heartfelt gratitude goes to my younger brother, Shahan, for taking my responsibilities on his shoulder since very young age. I also wish to express my warm and sincere thanks to my mother-in-law for her kindness and earnest wishes.

Last but not least, my wholehearted appreciation are due to my beloved wife, Fathima. The way she took care of me and our little princess, Zoharin, besides her own study and work, was really commendable. My study would not have been completed so smoothly without her patience and sacrifices. She stood by me in ups and downs, not only during my PhD study, but also in all stages of my life, and always endowed me with her endless love and support. My dear, you are very special.

Mostafa Wasiuddin Numan September 2017 Adelaide

## **Conventions**

The following conventions have been adopted in this thesis:

## **Typesetting**

This document was compiled using LATEX2e. Texmaker and TeXstudio were used as text editor interfaces to LATEX2e. Inkscape and Matlab were used to produce schematic diagrams and other drawings.

## Referencing

The Harvard style has been adopted for referencing.

## **System of units**

The units comply with the international system of units recommended in an Australian Standard: AS ISO 1000–1998 (Standards Australia Committee ME/71, Quantities, Units and Conversions 1998).

## **Spelling**

Australian English spelling conventions have been used, as defined in the Macquarie English Dictionary (A. Delbridge (Ed.), Macquarie Library, North Ryde, NSW, Australia, 2001).

## **Abstract**

This thesis investigates network on chip (NoC) architecture, most particularly, NoC mapping algorithms for homogeneous processing elements of a system on chip (SoC) designed for AI and cognitive computing.

Production systems are used in cognitive architectures and knowledge-based systems to produce appropriate reasoning behaviours by matching the symbolic information of the environment with the production rules stored in their knowledge bases. General purpose computers are not specifically manufactured for the purpose of continuous matching involved in production systems, and often fail to deliver the performance and speed required in real-time applications. A reconfigurable and parallel computer architecture, named the Street Processor, has been developed by the research group of which the author is a member, to address the performance gap. The processor has its own instruction set, called the Street language, to define the production rules. The production rules are implemented on simple and identical PEs of the Street Processor that conduct the matching operations in parallel and asynchronously. Special steps can be taken to make these operations synchronous if required. Two artificial agents demonstrate the capability of the Street Processor, and are also used as test cases to measure the performance of NoC mapping techniques.

The Street Processor is expected to contain thousands of fine-grained homogeneous PEs to build a complex cognitive agent. To make the continuous and simultaneous communication among the PEs more efficient, a regular and generic NoC architecture is considered in this work. The network architecture allows multiple PEs to be associated with a single NoC router to optimise its resources. The mapping of PEs to NoC routers, which is an NP-hard optimisation problem, is addressed in this work using two alternative approaches. The Branch and Bound (BB) and Simulated Annealing (SA) techniques are analysed for use as a preferred mapping technique. Although the BB technique provides a mapping solution faster than SA, the latter is considered more promising for large systems, e.g. the Street Processor, since BB achieves the computation time advantage at the cost of a high memory requirement.

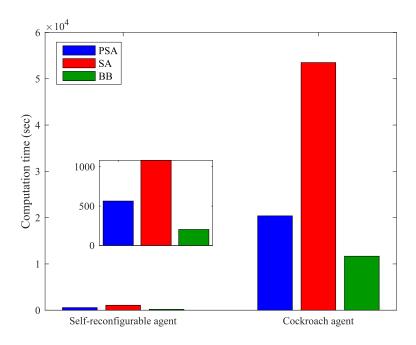

To reduce the computation time of the SA method by shrinking the search space, the dependency graph, which captures the communication volume among PEs over a period of time, is partitioned into smaller groups of PEs (GPEs). By assigning each GPE to a router, this approach also reduces the number of required routers and the interrouter traffic of the network. A Priority-based Simulated Annealing (PSA) technique is proposed, which takes advantages of the relative placements of the routers and interdependencies of the GPEs to determine a heuristic initial mapping to start annealing. The experiments show that this approach significantly improves the computation time for finding a solution without sacrificing mapping quality. Considering the inherent memory utilisation advantage over the BB technique, and the computation time improvement over the original SA technique, the proposed approach is suggested to be the most suitable for NoC mapping for the Street Processor and similar homogeneous SoCs.

## **List of Figures**

| 1.1  | Transistor counts in 1965 – 2015                                      | 3  |

|------|-----------------------------------------------------------------------|----|

| 1.2  | Thesis outline and contributions                                      | 8  |

|      |                                                                       |    |

| 2.1  | Block diagram of the Soar architecture                                | 20 |

| 2.2  | Soar processing cycle                                                 | 21 |

|      |                                                                       |    |

| 2.3  | Block diagram of the ACT-R architecture                               |    |

| 2.4  | Processing cycle of a production system                               | 25 |

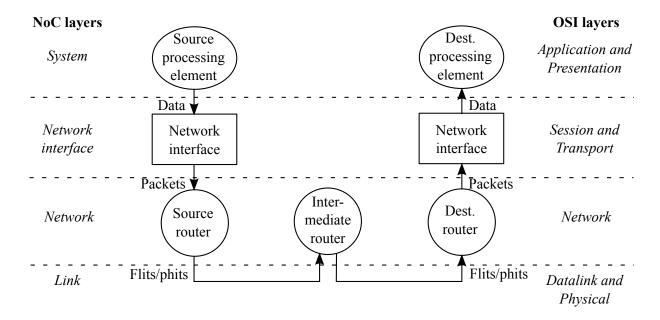

| 2.5  | Data flow through different layers in NoC and OSI models              | 32 |

|      |                                                                       |    |

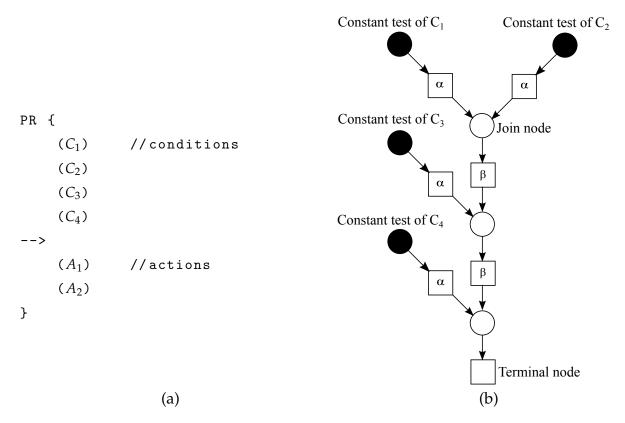

| 3.1  | An example of Rete discrimination network                             | 41 |

| 3.2  | A Street production rule                                              | 44 |

| 3.3  | Example of a inequality check                                         | 45 |

| 3.4  | Example of a negative condition element                               | 46 |

| 3.5  | Example of a negative action                                          | 47 |

| 3.6  | Example of multiple instantiation of a production rule                | 47 |

| 3.7  | A rule to demonstrate bundled actions                                 | 48 |

| 3.8  | A Street production rule susceptible to race conditions               | 49 |

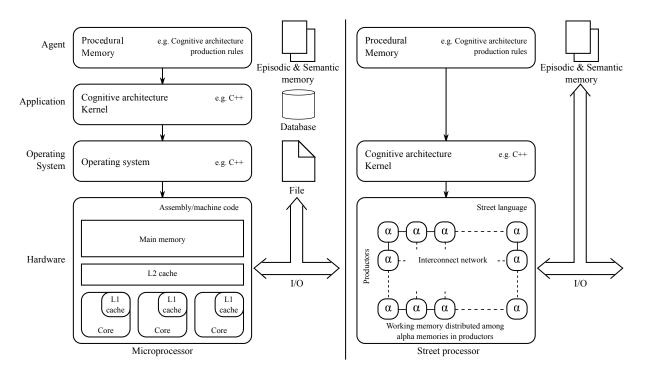

| 3.9  | Hardware and software stack on a conventional computer and the Street |    |

|      | Processor                                                             | 51 |

| 3.10 | Block diagram of a productor                                          | 51 |

| 3.11 | An example of a Big Productor                                         | 53 |

| 3.12 | An example of dependencies between two production rules               | 54 |

|      |                                                                       |    |

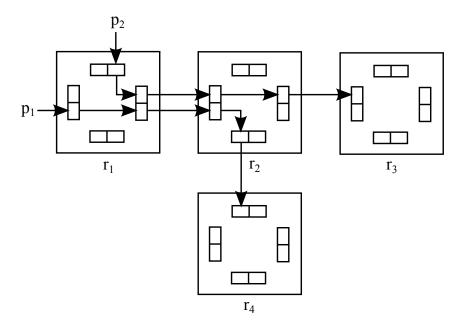

| 4.1  | A NoC structure and its major components                              | 60 |

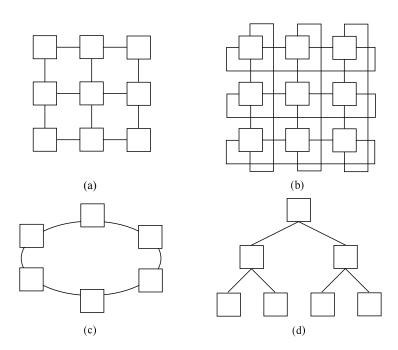

| 4.2  | Regular NoC topologies                                                | 61 |

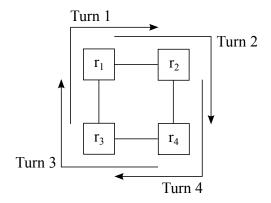

| 4.3  | A deadlock situation                                                  | 63 |

|      |                                                                       |    |

#### **List of Figures**

| 4.4  | Permitted turns in dimension order routing                                                | 64  |

|------|-------------------------------------------------------------------------------------------|-----|

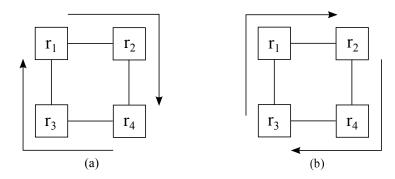

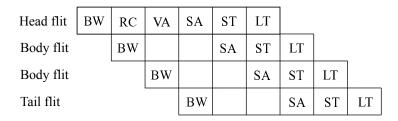

| 4.5  | Data decomposition in wormhole routing                                                    | 66  |

| 4.6  | Example of virtual channel flow control                                                   | 68  |

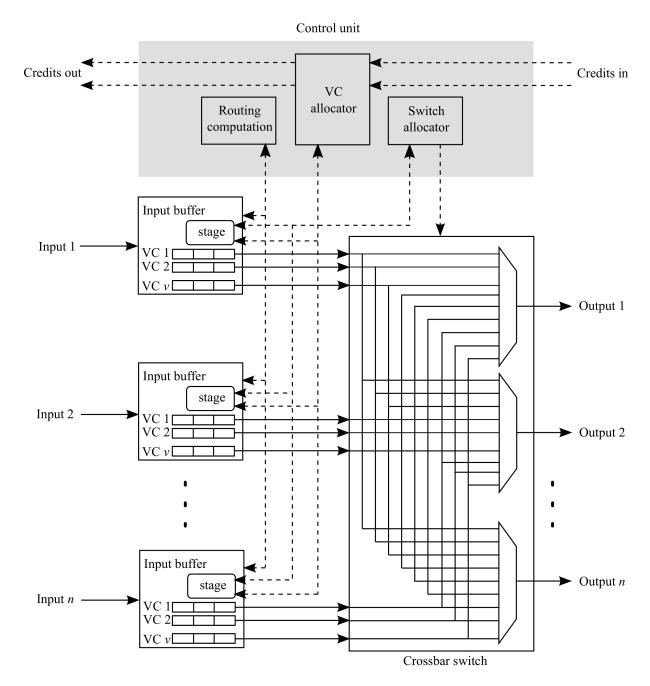

| 4.7  | Router micro-architecture with $n$ interfaces, each having $v$ virtual channels           | 69  |

| 4.8  | Pipeline stages of a NoC router                                                           | 70  |

|      |                                                                                           |     |

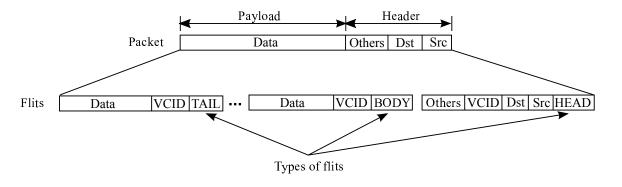

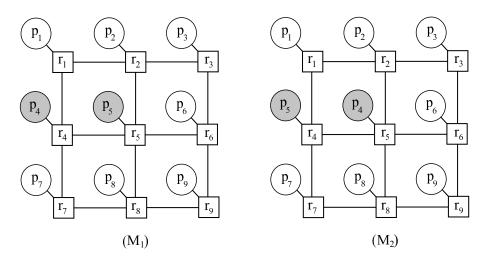

| 5.1  | Examples of two mappings $M_1$ and $M_2$                                                  | 77  |

| 5.2  | Simulated Annealing algorithm for NoC mapping                                             | 81  |

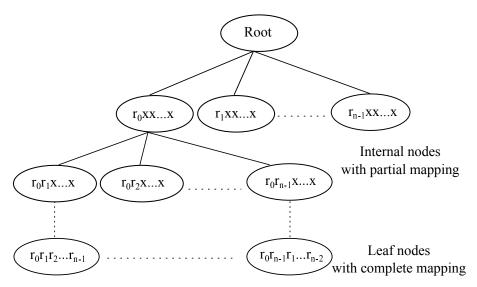

| 5.3  | An example of Branch and Bound search tree of solution space                              | 83  |

| 5.4  | Branch and Bound algorithm for NoC mapping                                                | 85  |

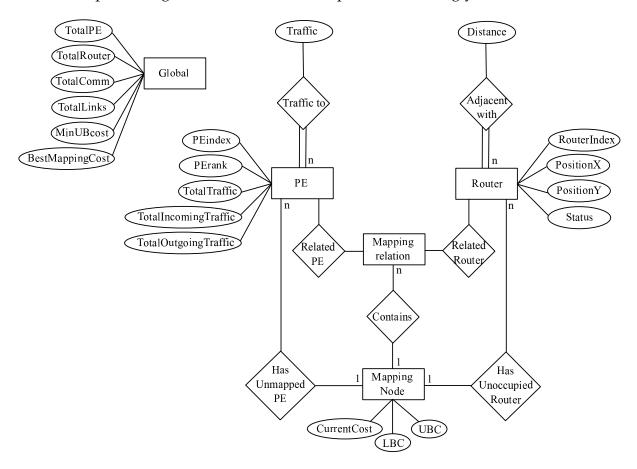

| 5.5  | Relationship between the major entities                                                   | 89  |

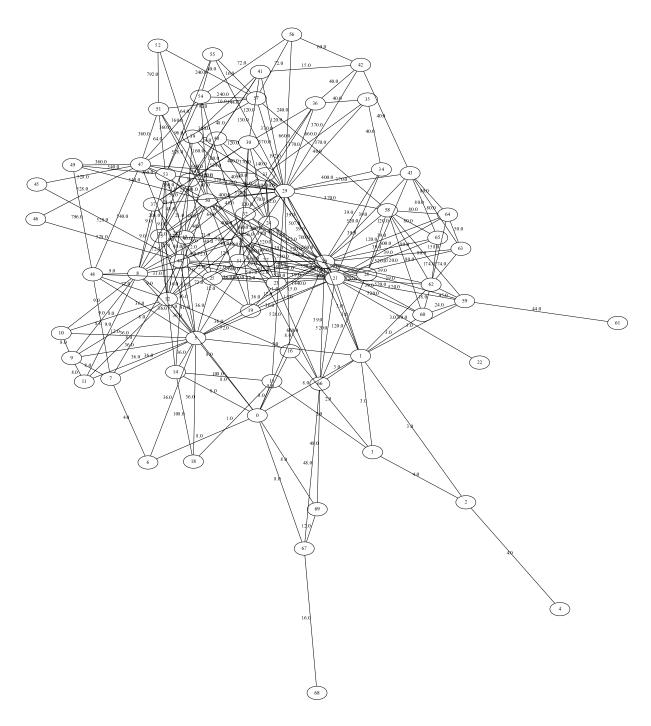

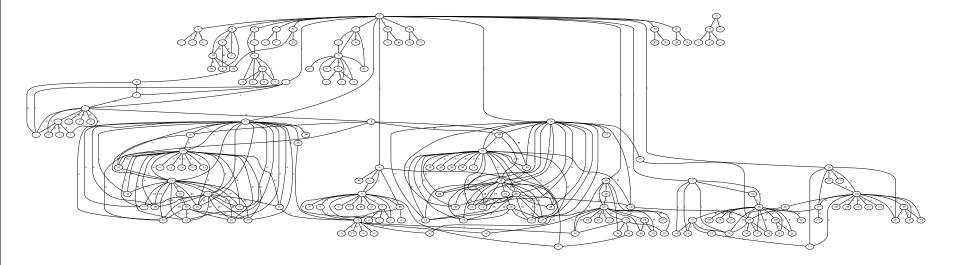

| 5.6  | Traffic graph of the agent solving Branch and Bound mapping                               | 91  |

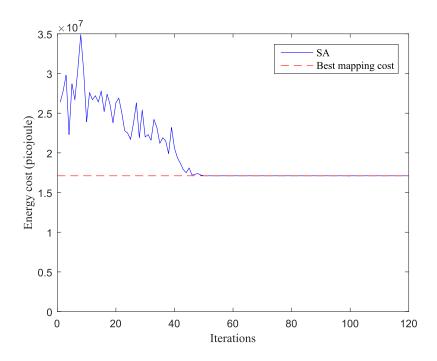

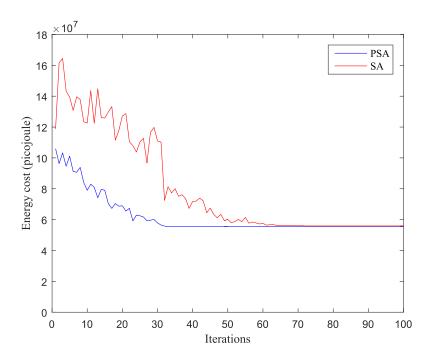

| 5.7  | Energy cost in each iteration of Simulated Annealing                                      | 92  |

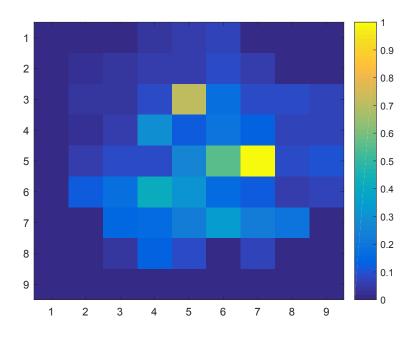

| 5.8  | Router-wise traffic after Simulated Annealing mapping                                     | 92  |

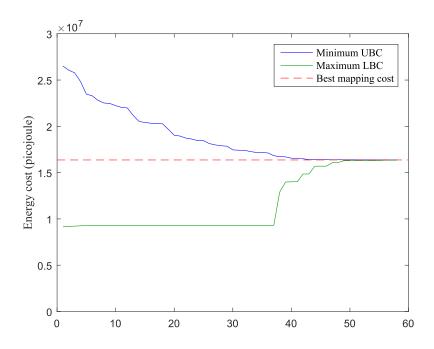

| 5.9  | Minimum UBC and maximum LBC limiting the best energy cost                                 | 93  |

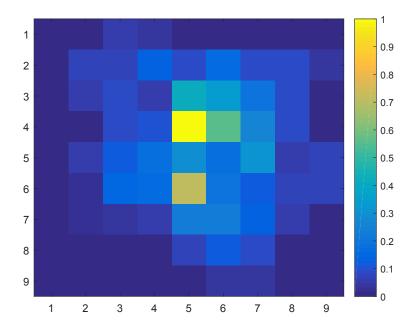

| 5.10 | Router-wise traffic after Branch and Bound mapping                                        | 94  |

| 5.11 | Energy cost comparison between SA and BB mapping                                          | 95  |

| 5.12 | Computation time comparison between SA and BB mapping                                     | 95  |

|      |                                                                                           |     |

| 6.1  | Example of graph partitioning                                                             | 100 |

| 6.2  | The phases of multi-level graph partitioning                                              | 101 |

| 6.3  | The collapse of an edge                                                                   | 102 |

| 6.4  | Priority-based Simulated Annealing algorithm for GPE mapping 1                            | 105 |

| 6.5  | Routers indicating their priorities in $5\times 5$ and $6\times 6$ network structures . 1 | 107 |

| 6.6  | Pseudocode of localised swap                                                              | 108 |

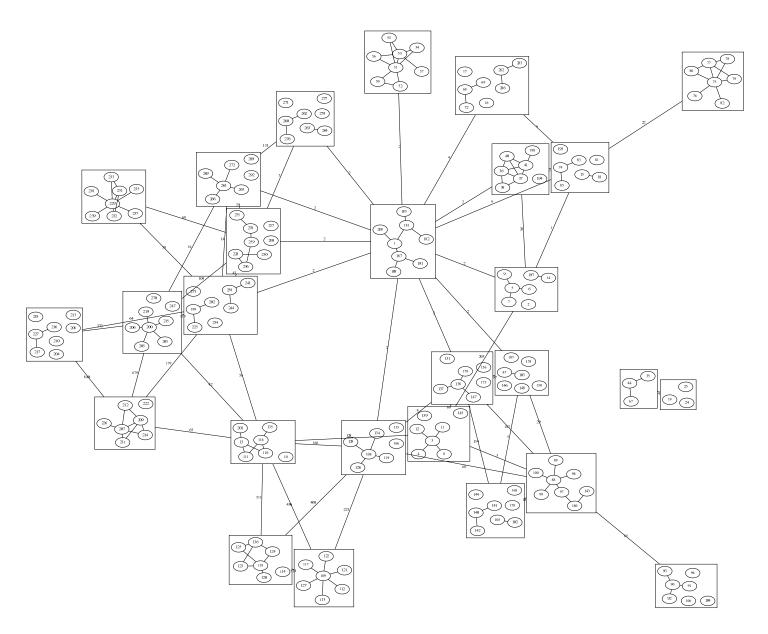

| 6.7  | Traffic graph of the Cockroach agent                                                      | 112 |

| 6.8  | Computation time comparison between mappings of two Street agents . 1                     | 113 |

| 6.9  | Partitioned traffic graph of the Cockroach agent                                          | 114 |

| 6.10 | Energy cost comparison between PSA and SA in each iteration for the                       |     |

|      | Cockroach agent                                                                           | 115 |

|      | List of Figures                                |

|------|------------------------------------------------|

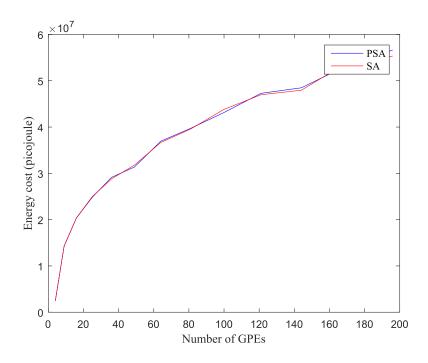

| 5.11 | Energy cost comparison between PSA and SA      |

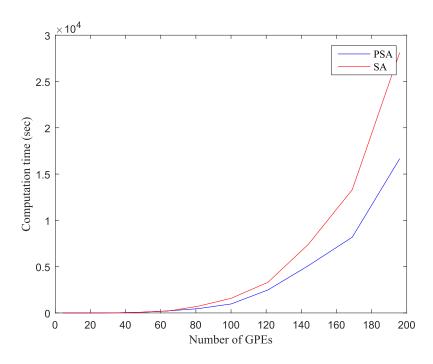

| 5.12 | Computation time comparison between PSA and SA |

|      |                                                |

|      |                                                |

## **List of Tables**

| 2.1 | Approaches to building AGI agents                                | 15             |

|-----|------------------------------------------------------------------|----------------|

| 2.2 | Classifications of cognitive architectures                       | 17             |

| 4.1 | Node table based routing of a $3 \times 3$ mesh using XY routing | 6 <sup>t</sup> |

| 5.1 | Important Street rules to realise the self-configurable agent    | 9(             |

| A.1 | List of Street production rules of the self-configurable agent   | 128            |

| B.1 | List of Street production rules of the Cockroach agent           | 132            |

## Chapter 1

## Introduction

HIS thesis considers on-chip communication networks for parallel computation using a production system programming model. The context and motivation for the research are explained in this chapter. It briefly describes the significance of networks on chip (NoCs) as a communication platform among hardware processing elements (PEs). The original contributions of the research are highlighted, and an overview of the thesis structure is presented in this chapter.

### 1.1 Background

Since Allen Newell, Herbert Simon and Cliff Shaw wrote the first artificial intelligence (AI) program in 1956 to mimic the problem solving skills of human beings, research activity aimed at achieving human-like intelligence has progressed along many streams. This includes knowledge-based systems (Hayes-Roth and Jacobstein 1994), genetic and evolutionary algorithms (Goldberg 1994, Jones 1998), fuzzy systems (Zadeh 1994), neural networks (Haykin 2001) and artificial general intelligence (AGI) (Goertzel and Wang 2007). While most of the approaches aim at a particular aspect or application of intelligence, AGI targets the implementation of an intelligence that can be applied in various domains. Cognitive architectures have been proposed as the most elegant way to achieve AGI in artificial systems (Langley 2006), and have been successfully applied to many applications (Anderson 1983, Laird et al. 1987, Anderson 1996). They capture knowledge and skills in systems to yield intelligent behaviours in a diversity of complex environments. Cognitive architectures commonly use production systems for knowledge representation and processing. In production systems, the knowledge is encoded in the form of production rules to achieve appropriate reasoning behaviour in accordance with the states of the environment in which the systems are running. Besides cognitive architectures, production systems are also applied in the implementations of different knowledge-based systems in areas including computer aided design (Chen et al. 2012), medical diagnosis (Shortliffe 2012) and adaptive support systems (Angelov 2013), just to name a few.

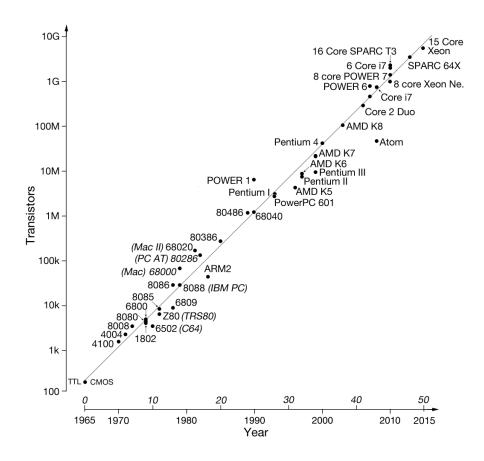

In the years since that first AI program, semiconductor fabrication technology has advanced to the point that it is possible to cost-effectively produce integrated circuits (ICs) containing billions of transistors. For three decades the exponential increase of transistor count followed Moore's law, and it is only in recent years that the rate of growth has started to slow as shown in Figure 1.1 (Scherer 2015). The performance demands of modern complex embedded applications have also increased substantially. These demands cannot be handled by the processors containing a single core or processing element. The technology growth and increasing performance demands have driven researchers to adopt a new paradigm, called the system on chip (SoC), in which an entire computational systems is realised on a single chip. For very large and complex systems, SoCs often contain multiple PEs, and are then known as multi-processor SoCs (MPSoCs) (Jerraya and Wolf 2004). The underlying concept of such systems is to

Chapter 1 Introduction

divide applications into sections that can be processed concurrently on multiple programmable PEs.

**Figure 1.1. Transistor counts in 1965 – 2015.** A plot of transistor counts per IC against year of introduction; the vertical line corresponds to exponential growth of transistor count doubling every two years (Scherer 2015).

The performance of SoCs is greatly dependent on the characteristics of the interconnection between the PEs, particularly as the number of PEs in the SoC increases. It is necessary to implement a communication infrastructure that provides the required communication bandwidth between PEs, while keeping latency low and minimising power consumption. Networks on chip have opened a new option for high performance on-chip communication (Dally and Towles 2001). NoCs consist of a chip-wide network of locally connected routers able to relay data from any PE on the network to any other. Compared to the conventional interconnect using shared buses and crossbars, they provide a flexible high performance chip-level communication with regularity and modularity. In the design flow of NoC architectures, the mapping of PEs onto NoC structures plays a crucial role because this affects the traffic flow within the NoC, and can have a significant effect on the overall performance of the system.

This thesis focuses on the implementation of a NoC-based communication infrastructure for a SoC containing specialised hardware for production systems that will implement a cognitive architecture for AGI. Critically, it also proposes an efficient algorithm to map the PEs onto the NoC structure.

#### 1.2 Research motivations

To achieve human-like intelligence, a system must possess a large bank of knowledge. Since the realisation of hard-coded knowledge is slow, tiresome and error-prone, intelligent systems often involve logical expressions of the pattern matching processes, known as production systems, which provide a straightforward mechanism to imply new knowledge using stored information (Nilsson 2014). Whenever the state of the environment changes they perform parallel pattern matching between the current state and remembered information, and trigger appropriate actions. Production systems are, by nature, computation-intensive because of the requirement for continuous parallel repeated searching and matching processes. The integration of a large knowledge base increases the demand on these processes (Hayes-Roth and Jacobstein 1994). However, the immature programming paradigm and tools for them make it harder for a programmer to achieve something in a production system compared with systems programmed using conventional languages. As a result, their performance has, historically, not been satisfactory for complex applications.

Most of the data manipulated by production systems is symbolic because of the ability of symbolic data to represent abstract information, which is one of the important aspects of intelligence (Newell and Simon 1976). Several customised hardware architectures were proposed to improve the efficiency of execution of production systems in the 1980s (Stolfo 1983, Gupta 1985), but these efforts faded away with the improved performance and availability of general purpose computers, and for many years production systems were largely realised on general purpose computers. With the inception of sophisticated intelligent agents, however the execution of production systems on general purpose machines has failed to deliver the performance and speed required in real-time applications. This limitation is expected to become more critical as cognitive architectures evolve towards being able to implement agents that achieve true AGI. However, the massive increase in the number of transistors now implementable

Chapter 1 Introduction

on one chip, and the evolution of the MPSoC model, have revived the interest in specialised hardware for large production systems that are subject to real-time time constraints.

Production systems usually spend most of their computation efforts matching the production rules with the state of the environment (Forgy 1979). For a conventional machine, this operation exhausts the available memory and processing resources, and makes the system slow. But the inherently parallel characteristics of production systems are a good match for the large scale parallel computation that can be achieved by multiple PEs integrated on a single IC. The improvement of semiconductor technology provides the ability to realise a hardware-based production system which involves fine-grained parallelism by associating each production rule to a PE, and thus achieving very high higher execution speeds.

NoCs have recently emerged as an effective communication platform for systems with a large number of PEs. They provide on-chip networks of routers to transmit data between PEs. The placement of PEs in the NoC network greatly influences the performance of the system because the communication time, link bandwidth and energy are dependent on it. But determining the optimal mapping of PEs to NoC routers is an NP-hard problem in which the search space increases factorially with the number of PEs and routers. It requires prohibitive computation time to solve using exhaustive algorithms (Garey and Johnson 1979). Therefore, an effective mapping algorithm is required to obtain an near-optimum mapping within a tolerable time limit. Branch and Bound (Lawler and Wood 1966) and Simulated Annealing (Kirkpatrick *et al.* 1983) are two optimisation approaches commonly used to solve this kind of problem. The work described in this thesis examines these approaches to propose an efficient NoC mapping algorithm for hardware-based production systems.

#### 1.3 Thesis objectives

This thesis studies the design of a hardware for production systems, which implements fine-grained parallelism in execution by evaluating production rules in simple homogeneous PEs. The objectives of the research reported in this thesis is to develop an efficient communication platform for the hardware. It targets NoC-based on-chip communication where each router can be associated with one or more PEs. The mapping of PEs to NoC routers is another problem that is also explored in this thesis. Branch and

Bound, and Simulated Annealing based mapping techniques are evaluated in order to propose an improved mapping algorithm. The next Section presents a summary of the original contributions made in the course of addressing these research issues.

## 1.4 Statement of original contributions

This thesis makes contributions in the area of on-chip communication of homogeneous PEs of cognitive workload. The contributions can be divided into two categories. The first part focuses on the design of a interconnect platform for homogeneous PEs of a hardware-based production system. And the second part concerns the mapping of PEs to NoC routers using optimised mapping algorithms.

#### 1.4.1 On-chip communication of cognitive workload

A conventional computer, with its sequential execution path and centralised memory, is not a good match for the computational requirements of cognitive agents. Rather, these would be better served by hardware that supports fine-grained parallelism and distributed memory, somewhat like the brain. The *Street Processor* is a reconfigurable, flat, parallel computer architecture designed as a SoC with many homogeneous PEs for symbolic cognitive workloads (Frost *et al.* 2015). It has own instruction set, called the *Street language*, to define the behaviour of an agent using production rules.

In this processor, thousands of identical PEs transmit data to each other simultaneously. This subsequently causes new data to be generated by the PEs when their corresponding production rules match the state of the environment, and this results in even more traffic. To make this traffic exchange feasible and efficient, a NoC-based communication platform is developed for this hardware. NoCs have been widely used in embedded heterogeneous SoCs, however no application is reported for event-driven SoCs containing such a large number of homogeneous PEs. Thus the application of NoCs in the class of parallel processors exemplified by the Street Processor is considered to be the principal contribution in this thesis. This work has been presented in *International Workshop on Artificial Intelligence and Cognition (AIC 2015)*, under the title of "A Network-based Communication Platform for a Cognitive Computer" (Numan *et al.* 2015).

Chapter 1 Introduction

#### 1.4.2 Optimised mapping techniques

Optimal mapping of PEs to NoC routers is an NP-hard problem which is a big challenge in NoC design. This work investigates mapping techniques based on two optimisation algorithms. Branch and Bound is a systematic approach, which reduces the search space by deleting unpromising partial solutions without further exploring them. On the other hand, Simulated Annealing is a probabilistic technique, which is designed to avoid the trap of becoming stuck at local optima. A comparative study of the mapping techniques based on these approaches is done in this work to contribute towards determination of a preferred approach of the proposed mapping algorithm.

The NoC mapping process is used as an example of a cognitive problem in this work. In order to support building a self-configurable agent, the Branch and Bound based mapping is itself implemented using Street language. This demonstrates that the Street Processor can dynamically and autonomously re-arrange the placement of PEs based on recent traffic history. The significance of this action is that it shows the capacity of the Street Processor to monitor and improve its own performance.

NoCs are more scalable than other contemporary on-chip communication platforms (Dally and Towles 2004). In this work, the scalability of NoCs is further improved by allowing multiple PEs to be associated with a single router. This consequently reduces the number of routers in a NoC structure and reduces the implementation cost. When the communication patterns include clusters of PEs with a lot of traffic between them, this strategy reduces the inter-router traffic of the network. This approach also shrinks the search space of the PE-to-router mapping problem since a group of PEs (GPE) are assigned to a router, instead of an individual PE. The mapping of GPEs to routers is achieved by an improved Simulated Annealing algorithm, which involves a heuristic initial mapping to expedite the process. This work is in preparation to be submitted to a peer-reviewed journal under the title of "Priority-based Network-on-Chip Mapping of the Processing Elements of Production Systems".

#### 1.5 Overview of the thesis

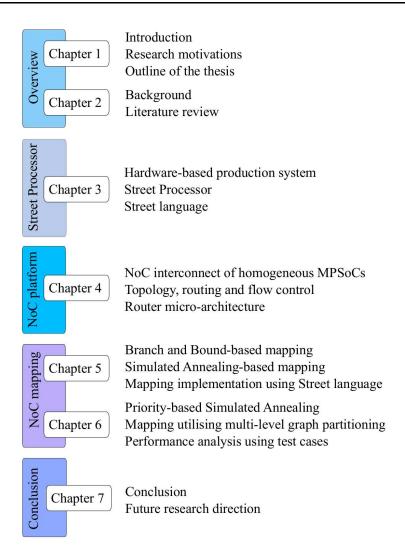

As outlined in Figure 1.2, this thesis comprises five parts including an overview of the work undertaken, a review on the Street Processor, two parts discussing the above-mentioned contributions and the conclusion. The highlights of each part of the thesis is presented as follows.

**Figure 1.2. Thesis outline and contributions.** This thesis is composed of 7 chapters in total, divided in five major parts. The major contributions lie in the part of NoC mapping.

Overview (Chapters 1 & 2) provides the introductory information, background and a review on the technologies relevant to this thesis. The current chapter has described the motivation, objective and contributions of the work performed in this study. Chapter 2 presents a literature review of the previous works in the fields of cognitive architectures, production systems and NoCs. This chapter also provides justification for the methodologies and approaches used in this work.

**Street Processor (Chapter 3)** reviews the design of a hardware-based production system. It describes the architecture of the Street Processor, containing many homogeneous PEs. The general structure of PEs are described in this chapter. The production rules are defined by the Street language which is also explained. This

Chapter 1 Introduction

chapter also introduces some promising features like sleep period and Big Productors that make the Street Processor a very novel on-chip production system.

**NoC platform (Chapter 4)** of the SoC with many PEs is presented in this part of the study. First, it presents the justification for using NoCs instead of traditional on-chip interconnect techniques in such systems. Second, a NoC-based communication platform is described for the class of SoCs containing large numbers of homogeneous PEs, represented by the Street Processor. This chapter discusses different aspects of NoC design e.g. topologies, routing schemes, flow control techniques, as well as the micro-architecture of a NoC router.

NoC mapping (Chapters 5 & 6) presents several techniques for mapping homogeneous PEs onto NoC structures. Chapter 5 describes two mapping techniques using Branch and Bound, and Simulated Annealing algorithms. It also demonstrates the comparison between these two techniques. In addition, the Branch and Bound mapping algorithm is implemented using Street language demonstrating the feasibility of constructing self-configurable cognitive agents. In Chapter 6, an improved Priority-based Simulated Annealing algorithm is proposed, which finds an optimum mapping solution in a reasonable computation time without sacrificing mapping quality. The performance of this technique is analysed using two test cases as well as a set of synthetic traffic scenarios.

**Conclusion (Chapter 7)** summarises the significance of the work, results and contributions presented in this thesis. This chapter also presents an outlook of possible future research work and improvements.

## Chapter 2

## Background and Related Work

HE use of production systems is very common in cognitive architectures because of their ability to produce effective reasoning behaviour, and simple and regular structure. In spite of being the subject of research for many years, production systems have been limited by their slow performance. Researchers have proposed different algorithms to mitigate this problem and have implemented these algorithms on a variety of hardware systems from conventional computers to systems on chip. SoCs with multiple processing elements have emerged as a promising technology to implement large and complex systems. However, efficient communication between the PEs still poses challenges to researchers. Networks on chip are an efficient solution for on-chip communication, but mapping of PEs onto NoC routers strongly influences the performance of SoCs and is an important area of research. This chapter provides a study on background and related works on cognitive architectures, production systems, NoCs and other related topics to establish the context for the work described in this thesis.

#### 2.1 Introduction

Human-like intelligence in artificial systems, commonly termed as artificial general intelligence in the literature, is a very long studied area of research. In contrast to advanced AI systems such as Deep Blue (Campbell *et al.* 2002) and Watson (Ferrucci *et al.* 2010), which are very expert in specific applications, AGIs are conceived to solve general problems (Thorisson and Helgasson 2012). AGI agents are expected to have human-level intelligence, general knowledge across different domains, the ability to reflect on themselves and the ability to create fundamental innovations and insights (Franklin 2007).

Several approaches have been adopted to achieve AGI in a system, but no one artificial system has been able to approach the level of human intelligence. One of the most promising fields of research directed to this end is cognitive architectures. Cognitive architectures are large systems of heterogeneous modules and components, which operate coherently to solve general problems in multiple domains (Thorisson and Helgasson 2012). As a foundation for AGI systems, they have those characteristics of agents that are common to multiple application domains. They include memories that store information and representation of the agent's goals and knowledge. They also contain well defined processes to interact with the environment, and learning mechanisms to improve their performance over time.

Many cognitive architectures (Forgy 1979, Anderson 1996, Kieras and Meyer 1997) involve production systems as the core of their reasoning because of their ability to describe how humans think. They receive inputs from the environment and compare these against a knowledge base to deliver appropriate responses. They have been generally considered computationally expensive and slow, and hence were largely ignored in industry (Kuo and Moldovan 1992), in spite of their immense promise to support general purpose intelligent systems. But the increasing demand of intelligent systems is continuously pressing to build efficient production systems.

Research on production systems has been pursued in different directions. Most of these efforts considered implementation of production systems on conventional computers. These implementations are prone to under-utilisation of available resources due to the von Neumann bottleneck (Backus 1978). With the continuous evolution of

semiconductor process technology, SoCs with multiple PEs have evolved as an efficient solution to this bottleneck for many applications (Jerraya and Wolf 2004). Communication between the on-chip components of MPSoCs has been a broad area of research ever since the MPSoC concept emerged. It is evident that shared bus and ad hoc point-to-point connection based solutions could not support the ever-increasing communication demand of MPSoCs. NoCs, inspired by wide area networks of computers, emerged as a potential solution and opened a new paradigm of on-chip communication (Dally and Towles 2001). The performance of SoCs is influenced by the placement of PEs on the NoC infrastructure. This encouraged researchers to propose efficient algorithms to solve this placement problem.

This chapter starts with a short history of AGI systems in Section 2.2. This is followed by a discussion of cognitive architectures in Section 2.3 that highlights their characteristics and provides a category-wise review of cognitive architectures. This section also briefly describes the two most successful cognitive architectures: Soar (Laird *et al.* 1987, Laird 2012) and ACT-R (Anderson 1996, Anderson *et al.* 2004) , which are both based on production systems. Section 2.4 describes the basic structure of production systems and reports a study on state of the art techniques. Section 2.5 explores SoCs with multiple PEs as the most appropriate implementation technique for complex embedded systems. Finally, Section 2.6 presents the communication model and a review on the architectures of NoCs. The algorithms for the placement of PEs on NoCs structure are also reviewed in this section.

## 2.2 Artificial general intelligence

An AGI is a system that could successfully performs a wide range of tasks autonomously across different domains in a similar way to a human being. The features that distinguish AGI agents from other AI agents are their abilities to pursue a wide variety of goals embedded in different environments rather than solving a predefined problem. The original aim of AI research was to build human level intelligence. Herbert Simon, who was one of the founders of the concept of AI, forecast about Turing's 'Thinking machine' (Turing 1950) that "... their ability to do these things is going to increase rapidly until – in a visible future – the range of problems they can handle will be coextensive with the range to which the human mind has been applied" (Simon and Newell 1958). AI research started towards this goal, but in 1970s - 1980s, it was realised

that the practical problems in achieving this ambitious goal in reality were immense, perhaps intractable. As a consequence, AI researchers cut back their objectives to develop intelligent systems with domain specific targeted solutions, called 'weak AI' to contrast with the 'strong AI' of general artificial intelligence.

Recently, there has been a renewed interest in building human-like intelligent systems. Large corporations like Yahoo, Google, IBM, Facebook are investing in AGI related technologies. Google has acquired 'DeepMind', which builds general purpose learning algorithms for simulations, e-commerce, and games (Shu 2014). Motivated by the human nervous system, IBM introduced self-managed computer systems, called 'autonomic systems', which are able to configure themselves to optimise performance and to protect themselves from attacks (IBM 2005). Yahoo and Facebook are also taking similar interest in this advanced AI technologies (Zacks 2013, Cutler 2014). Government organisations have also begun to develop an interest in strong AI. Intelligent distribution agent (IDA) is an AGI software agent of U.S. Navy that interacts in natural languages and assigns tasks to the pool of personnel autonomously (Franklin 2003).

No particular focus has yet emerged from current AGI research; rather contemporary projects are diverse and often pioneering in nature. This is because, interestingly, there is little consensus on the objective of reproducing 'intelligence' as a whole in computers. Although every approach gets its motivation from the same source, human intelligence, here 'intelligence' is understood in several senses. Consequently, researchers attempt to replicate different aspects of human intelligence. Table 2.1 lists different approaches to achieving human-level intelligence. Among them, cognitive architectures are considered to be one of the most promising approaches to create AGI systems (Pei 2007).

### 2.3 Cognitive architectures

John Anderson first coined the term 'cognitive architecture' in his book, "The architecture of cognition" (1983). He defined it to be 'the basic principles of operations of a cognitive system'. However, even before he introduced the concept, the idea was implicit in the rule-based information processing theories of Newell and Simon (1972). Newell further elaborated this concept in his book, "Unified theories of cognition" (1990), where he listed a number of important features of cognitive systems including adaptive, dynamic and flexible behaviours, learning, knowledge integration, vast

Table 2.1. Approaches to building AGI agents.

| Aspects     | Inspiration           | Rationale                      | Examples               |

|-------------|-----------------------|--------------------------------|------------------------|

| Structure   | Neuroscience, biology | Since intelligence is produced | TrueNorth              |

|             |                       | in human brains, an intelli-   | (Merolla et al. 2014), |

|             |                       | gent computer should simu-     | SyNAPSE (Srinivasa     |

|             |                       | late brain structure as faith- | and Cruz-              |

|             |                       | fully as possible              | Albrecht 2012),        |

|             |                       |                                | HTM (Hawkins and       |

|             |                       |                                | George 2006)           |

| Interaction | Linguistics           | Intelligence is displayed by   | Turing test (Turing    |

|             |                       | effective communication be-    | 1950)                  |

|             |                       | tween two parties. For this    |                        |

|             |                       | reason, an intelligent system  |                        |

|             |                       | should interact exactly like a |                        |

|             |                       | human                          |                        |

| Capability  | Domain-specific com-  | Problem-solving capability     | Deep blue              |

|             | puter applications    | proves intelligence. Hence,    | (Campbell et al.       |

|             |                       | an intelligent system should   | 2002), expert sys-     |

|             |                       | be able to solve certain       | tems (Jackson 1986)    |

|             |                       | practical problems that are    |                        |

|             |                       | currently solvable by humans   |                        |

|             |                       | only                           |                        |

| Behaviour   | Psychology            | Intelligence is associated to  | Soar (Laird et al.     |

|             |                       | cognitive behaviours that      | 1987), ACT-R           |

|             |                       | human beings demonstrate,      | (Anderson 1996)        |

|             |                       | such as perceiving, reason-    |                        |

|             |                       | ing, learning and acting.      |                        |

|             |                       | Therefore, an intelligent      |                        |

|             |                       | computer should reproduce      |                        |

|             |                       | these behaviours               |                        |

| Principle   | Logic, mathematics    | Intelligence is a form of ra-  | AIXI (Hutter. 2004),   |

|             |                       | tionality or optimality. So    | NARS (Wang 1995)       |

|             |                       | an intelligent system should   |                        |

|             |                       | always do the right thing      |                        |

|             |                       | according to certain general   |                        |

|             |                       | principles                     |                        |

knowledge base and real-time performance. These features were subsequently analysed and partially applied by several architectures (Anderson and Lebiere 2003).

# 2.3.1 Characteristics of cognitive architectures

All cognitive architectures are expected to demonstrate the ability to analyse the external and internal environment in order to solve both repeating and new problems by learning from experience. The essential characteristics of cognitive architectures are discussed here, some of which are adopted from (Langley *et al.* 2009b).

**Identification of events:** A cognitive architecture has the ability to identify events and match them with the known or familiar knowledge. This is the initial step in categorising events to determine appropriate responses to them. A cognitive architecture supports this feature by representing patterns of events. Production systems (Forgy 1979, Miranker 1987) of cognitive architectures perform this task through the use of conditions in their production rules.

Selection from alternatives: Often, multiple patterns in the knowledge base can be matched by the events. A cognitive architecture selects the most appropriate one from these alternatives. This decision making, known as *conflict resolution*, involves several criteria depending on architectures (Luger 2004, Miranker *et al.* 1990). A good cognitive architecture refines these criteria based on its experiences.

**Problem solving strategy** Human-like intelligent agents are most likely to handle new situations. This requires plans and problem solving mechanisms (Langley *et al.* 2009a). A cognitive architecture represents a plan as an ordered set of actions, their expected effects, and the manner in which these effects enable later actions.

**Remembering and learning:** A cognitive architecture encodes and stores the results of cognitive processing in memory, usually referred to as *episodic memory*, to retrieve them when required. An ideal cognitive architecture should also have some ways of learning to improve its performance by generalising specific experiences (Laird 2012).

**Knowledge sharing:** A cognitive architecture should be able to communicate with others agents so that they can obtain and share knowledge (Ferguson and Allen

Memory type Representative architecture Symbolic Rule-based memory Soar (1987), EPIC (1997) Graph-based memory SNePS (2007) Connectionist Globalist memory IBCA (2000) Localist memory Cortronics (2007) Hybrid Localist-distributed memory CLARION (2006) Symbolic-connectionist memory ACT-R (1996)

Table 2.2. Classifications of cognitive architectures.

2011). This may also require a way for transforming the knowledge from internal representations to a form suitable for communication.

Occasional uncertainty: Like human beings, a cognitive architecture may allow occasional uncertainties in its operations. This allows it to explore new experiences which might result in it learning new things. This type of learning is considered by some researchers to be an essential feature required to achieve cognition (Sun 2001).

# 2.3.2 Related work on cognitive architectures

In this section, cognitive architectures are reviewed and compared from different perspectives (Thorisson and Helgasson 2012, Langley *et al.* 2009b, Duch *et al.* 2008). Knowledge representation is considered a key property that can be used to differentiate cognitive architectures. An architecture achieves knowledge from the information stored in its memory. Various types of memory keep information about the environment, current activities and previous experiences. The importance of memory has been demonstrated from different perspectives in the recent literature (Hecht-Nielsen 2007, Hoya 2005, Hawkins and Blakeslee 2004). Based on the types of memories, cognitive architectures can be broadly divided into three categories: *symbolic*, *connectionist* and *hybrid* architectures, as summarised in Table 2.2.

#### Symbolic cognitive architectures

Symbolic architectures focus on information processing in a top-down analytic approach using high level symbols or declarative knowledge. They have the ability to input, output, store and alter symbolic entities, and to carry out appropriate actions to reach their goals. Soar (Laird *et al.* 1987), EPIC (Kieras and Meyer 1997), ICARUS (Langley *et al.* 2009a) and SNePS (Shapiro *et al.* 2007) are some prominent symbolic cognitive architectures. In symbolic architectures knowledge can be embedded in production systems as production rules (Laird *et al.* 1987). Production rules provide a flexible and context dependent representation of knowledge with their conditions matching the current state and actions modifying it. Production systems are discussed in more detail in Section 2.4. The knowledge can also be represented using directed graphs like semantic networks, conceptual graphs and schemata (Sowa 1992, Minsky 1974).

#### Connectionist cognitive architectures

Connectionist architectures have been widely used to solve domain specific problems. Less commonly they have also been used as the basis for general cognitive architectures. These architectures view knowledge as being encoded into simple neuron-like processing nodes. The nodes use low level activation signals flowing over a network that interact with each other in a specific way changing their internal states and revealing interesting emergent properties. The multi-layer perceptron and other neural networks based on delocalised transfer functions process information in a distributed, global way (O'Reilly and Munakata 2000). All parameters of such networks influence their outputs. On the other hand, the basis set expansion networks that use localised functions are examples of localist networks (Blachnik and Duch 2008, Duch *et al.* 2001). The output signals for a given input depend only on a small subset of units that are activated. This kind of architecture has been criticised in the literature for not demonstrating the desired functionalities of cognitive architectures (Langley *et al.* 2009b). IBCA (O'Reilly and Munakata 2000) and Cortronics (Hecht-Nielsen 2007) are two examples of connectionist architectures.

#### Hybrid cognitive architectures

Hybrid architectures result from combining the symbolic and connectionist paradigms of cognitive architectures. Symbolic architectures are able to process information and realise high level cognitive functions, whereas connectionist architectures are better

suited for capturing context specific behaviour and handling many pieces of low level information simultaneously. The potential benefit of a combined approach is therefore to have each method address the limitations of the other, allowing creation of a complete intelligent system architecture that covers all levels of cognitive processing. The localist-distributed class of hybrid architectures comprises a combination of localist modules with each concept specified by one processing node and distributed modules with each concept represented by a set of overlapping nodes. In comparison, the symbolic-connectionist class involves a mixture of symbolic modules (rule or graph based memory) and connectionist modules (localist or distributed type) (Sun and Alexandre 2013). ACT-R (Anderson *et al.* 2004), CLARION (Sun 2006) and DUAL (Kokinov 1994) represent the most successful hybrid cognitive architectures.

Many of the proposed architectures in the literature have been abandoned due to their limitations, while others have been vigorously pursued. Soar and ACT-R are the most successful and mature cognitive architectures. The following sections briefly discuss these two architectures.

#### 2.3.3 Soar

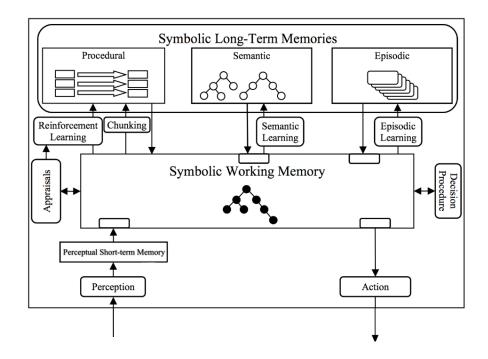

Soar (State, Operator And Result), one of the most successful symbolic cognitive architectures, has been gradually developed and extended over the last three decades (Laird *et al.* 1987, Laird 2012). It is a typical example of rule-based architectures designed to model general intelligence. Soar stores its procedural knowledge in the form of *production rules*, arranged in terms of operators. The *operators* act in the problem space that is the set of *states* in order to achieve the goal or *result*. Figure 2.1 shows the block diagram of the Soar architecture (Laird 2012).

The current version of the Soar architecture includes different types of memories that interact during its processing cycle. These are the short term *working memory*, and long term *semantic*, *procedural* and *episodic memories*. These memories are briefly described here:

**Working memory** stores information about the current state of the environment. The working memory elements (WMEs) are either supplied by sensors or copied from other memories based on relevancy to the present state. Working memory also contains an activation mechanism indicating the relevance and usefulness of WMEs.

Figure 2.1. Block diagram of the Soar architecture. (Laird 2012)

**Semantic memory** keeps declarative information and facts about the problem space. Knowledge is retrieved from semantic memory via deliberate associative retrieval i.e., using appropriate cues. Most of the knowledge is initialised from an existing knowledge base and the rest is acquired when new information is learned.

**Episodic memory** stores the memory episodes that a Soar agent has experienced. It includes contextualised information about specific events. This provides the agent with the ability to use prior experiences to handle the current state.

**Procedural memory** stores the production rules that support the proposal, evaluation, selection and application of operators during processing cycles. The operators act on the problem space and make changes to working memory.

The execution of a Soar agent is governed by its *processing cycle* in which the agent chooses an appropriate operator based on the information of its working memory and production rules. This cycle can be broken into five phases as shown in Figure 2.2. In the input phase, Soar receives the changes of current state to the perception block and a perceptual buffer in working memory is updated. In the next phase, the current state is elaborated by firing the production rules in parallel that match the changes to retrieve information relevant to that state. Then the operators are proposed by production rules

for the current state. Once operators are proposed, other rules register preferences for them based on different criteria such as frequency or recency of rule firings. The operators are then evaluated based on preferences by a fixed decision procedure, and if a single operator is unambiguously preferred by the evaluation criteria, it is selected for application. In the application phase, the selected operator is applied to make changes to the state in order to move the agent closer to its goal. Finally, in the output phase, Soar sends information of state changes to problem space via its actuators.

Figure 2.2. Soar processing cycle.

The Soar processing cycle repeatedly proposes, selects, and applies operators to a state. However, when knowledge about operator selection is insufficient to uniquely determine the appropriate operator to apply, an *impasse* occurs. When an impasse occurs, Soar decomposes the state into a *substate* that includes the reasons for the impasse and the state that the impasse arose in. From the perspective of the new state, the earlier state is known as the superstate. In the substate, operators are proposed, selected and applied in the same way as the superstate. Additional impasses may be encountered in a substate. This may lead to a stack of substates. Soar applies operators on states in the substates to resolve the impasse. When it is resolved, all the subsequent substates below it disappear and Soar learns new information. The reason for the impasse and its actions are then converted to production rules which summarise the processing that resolved the impasse. This learning process is known as *chunking* (Laird *et al.* 1986). The new production rules generated by chunking are added to the procedural memory to be used directly in similar situations in the future without creating substates.

A variety of complicated agents have been developed using Soar. The most visible has been TAC-Air-Soar that is used for training fighter pilots of U.S. Army (Tambe *et al.*

1995). Soar is also used in interactive computer games (Magerko *et al.* 2004), modeling human language processing (Lewis 1993) and categorisation (Miller and Laird 1996).

#### 2.3.4 ACT-R

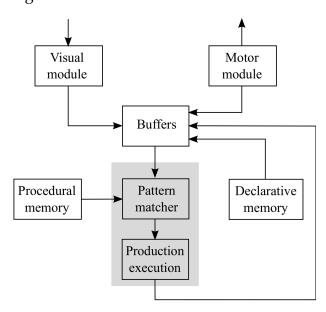

ACT-R (Adaptive Control of Thought-Rational) is a hybrid cognitive architecture that is concerned primarily with modelling human cognition (Anderson 1996, Anderson *et al.* 2004). It was developed based on a human associative memory (HAM) model (Anderson and Bower 1973) which was later extended into the model of human cognition (Anderson 1983). ACT-R architecture is composed of *modules, memories, buffers* and a *pattern matcher*. Figure 2.3 shows the high level architecture of ACT-R.

Figure 2.3. Block diagram of the ACT-R architecture. (Budiu 2013)

**Modules:** ACT-R is organised into a set of modules, each of which processes a different type of information to take care of the interface with the environment. The most well developed modules are sensory modules for visual processing and motor modules for actions.

**Memories:** There are two kinds of long term memories in ACT-R: *declarative memory* encodes factual knowledge about the environment into chunks (different from 'chunks' in Soar); and *procedural memory* coordinates the processing of the modules using its production rules. Both are realised as a symbolic-connectionist structure, where the symbolic level consists of production rules and chunks, and the sub-symbolic level of a massively parallel connectionist structure.

**Buffers:** ACT-R accesses its modules through buffers. For each module, a dedicated buffer serves as the interface with that module. The contents of the buffers collectively comprise the short term memory.

**Pattern matcher:** The pattern matcher searches for a production rule that matches against the contents of short term memory. Only one such rule can be executed at a given moment. That rule, when executed, modifies the buffers and thus changes the state of the system.

Each declarative chunk has an associated base activation that reflects its past usage and influences its retrieval from long term memory, whereas each production rule has an expected cost and probability of success. These enable an analytic characterisation of connectionist computations to measure the general usefulness of a chunk and production rule. These parameters influence the rule matching process of the pattern matcher that searches for a production rule to match against the state of the buffers. If several rules match, ACT-R computes the utility for each matched rule as the difference between its expected benefit and its expected cost. The system selects the production rule with the highest utility and executes its action. That action alters the buffers and thus changes the state of the system. This change causes new production rules to be matched and results in even more changes. Some changes modify existing structures, whereas others initiate actions in the associated modules, such as executing a motor command or retrieving a chunk from long term declarative memory.

ACT-R learns declarative knowledge through problem solving. The base activation for declarative chunks increases when they are used by production rules, and decreases otherwise. Similarly, the cost and success probability for productions is updated based on their observed behaviour. The architecture can learn entirely new rules from sample solutions through a process of production compilation that analyses dependencies of multiple rule firings, replaces constants with variables, and combines them into new conditions and actions (Taatgen 2005).

Over the years, a number of applications have been developed based on ACT-R model for understanding a variety of phenomena from the experimental psychology literature, including aspects of memory, attention, reasoning, problem solving and language processing. Anderson related ACT-R modules to different areas of the brain and developed models that match results from brain-imaging studies (Anderson 2007). It has been used in natural languages (Budiu and Anderson 2004), complex problem solving

(Byrne and Kirlik 2005), tutoring (Koedinger *et al.* 1997) and controlling mobile robots that interact with humans (Trafton *et al.* 2005).

# 2.4 Production systems

Soar, ACT-R and many other cognitive architectures such as EPIC (Kieras and Meyer 1997), CLARION (Sun 2006) and NARS (Wang 1995, Wang 2006) use production systems as a core mechanism to achieve their goals. A production system is one whose knowledge base contains the domain knowledge encoded in the form of rules to mimic human reasoning. It stems from the observation that much of human reasoning can be expressed by a set of *if-then* or *condition-action* rules. Instead of representing knowledge in a declarative and static way, a production system represents it in a general way to handle different situations.

# 2.4.1 Basic structure of production systems

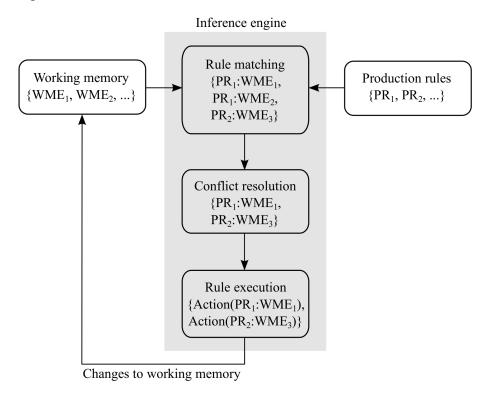

A production system generally consists of three components: a set of *production rules* to define behaviours, a global knowledge base, referred as *working memory*, representing the environment and a control mechanism called the *inference engine*.

**Production rules** consist of a left hand side (LHS) of conditions and a right hand side (RHS) of actions. If the condition part is matched with the current state of the environment, then the action part is executed. Each rule represents some knowledge about the problem solving process.

**Working memory** is the total knowledge base of the current state of the environment. It is represented as a set of attributes defining the domain world. The attributes are called WMEs, which are symbolic triples (e.g. (ID1, HasA, Tail) arranged in a graph data structure.

**Inference engine** The inference engine is a sequential program that controls the processing of the production system. It has three steps: rule matching (*match*), conflict resolution (*select*) and rule execution (*act*). The inference engine is said to be operating in forward chaining when the system starts in an initial state and executes production rules to reach the final state. A backward chaining system

starts at the goal state and tries to find the possible conditions that resulted in that state. Backward chaining is often used for learning, while forward chaining is common in reasoning (Rich and Knight 1991). In this research, the inference engine is considered in forward chaining only.

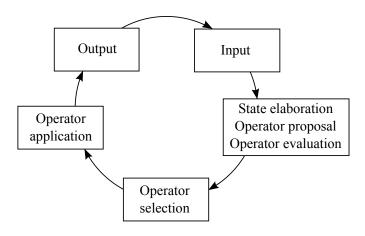

The schematic of Figure 2.4 shows the execution cycle of a production system that works on production rules and working memory, and is dictated by the steps of the inference engine.

**Figure 2.4. Processing cycle of a production system.**  $PR_1 : WME_1, PR_1 : WME_2$  and  $PR_2 : WME_3$  are three rule instantiations.  $Action(PR_1 : WME_1)$  and  $Action(PR_2 : WME_3)$  are the actions for the instantiations  $PR_1 : WME_1$  and  $PR_2 : WME_3$  respectively.

**Rule matching:** When the WMEs in working memory match the conditions of a production rule, the rule is *instantiated*. The rule may match multiple sets of WMEs at the same time, resulting in a *conflict set* of instantiations. For example, if  $PR_1$  is satisfied by both  $WME_1$  and  $WME_2$ , then there are two instantiations of  $PR_1$  and they create a conflict set.

**Conflict resolution:** In conflict resolution, a single rule instantiation is selected from the conflict set based on a variety of criteria. The criteria may be simple, such

as selecting the fist rule activated in the match phase, or may involve complex rule selection heuristics. In many cases, the activation is selected according to the recency of the matched WMEs in the working memory. This comes from the assumption that more recent matches are more likely to be relevant to the agent's current situation (Luger 2004, Miranker *et al.* 1990). It is also intended to guide the agent towards following a single line of reasoning. In Figure 2.4, *PR*<sub>1</sub> is selected for execution in the conflict resolution step.

**Rule execution:** Once a rule instantiation is selected, it *fires*, i.e. the action part of the production rule executes. This makes changes to working memory by adding, removing or modifying WMEs. The changes in working memory affect new rules and cause the cycle to begin again.

# 2.4.2 Related work on production systems

There is a long history of research on production systems. They were extensively investigated during the 1980s and 1990s (Kuo and Moldovan 1992) but they were considered to be computationally expensive and slow due to the underlying matching process. This encouraged the researchers to improve the performance and resource managements of production systems in different ways. The research efforts on production systems can be classified into three categories: *sequential matching*, *parallel matching* and *parallel rule firing* algorithms.

# Sequential matching algorithms